Altera 软件¶

Quartus¶

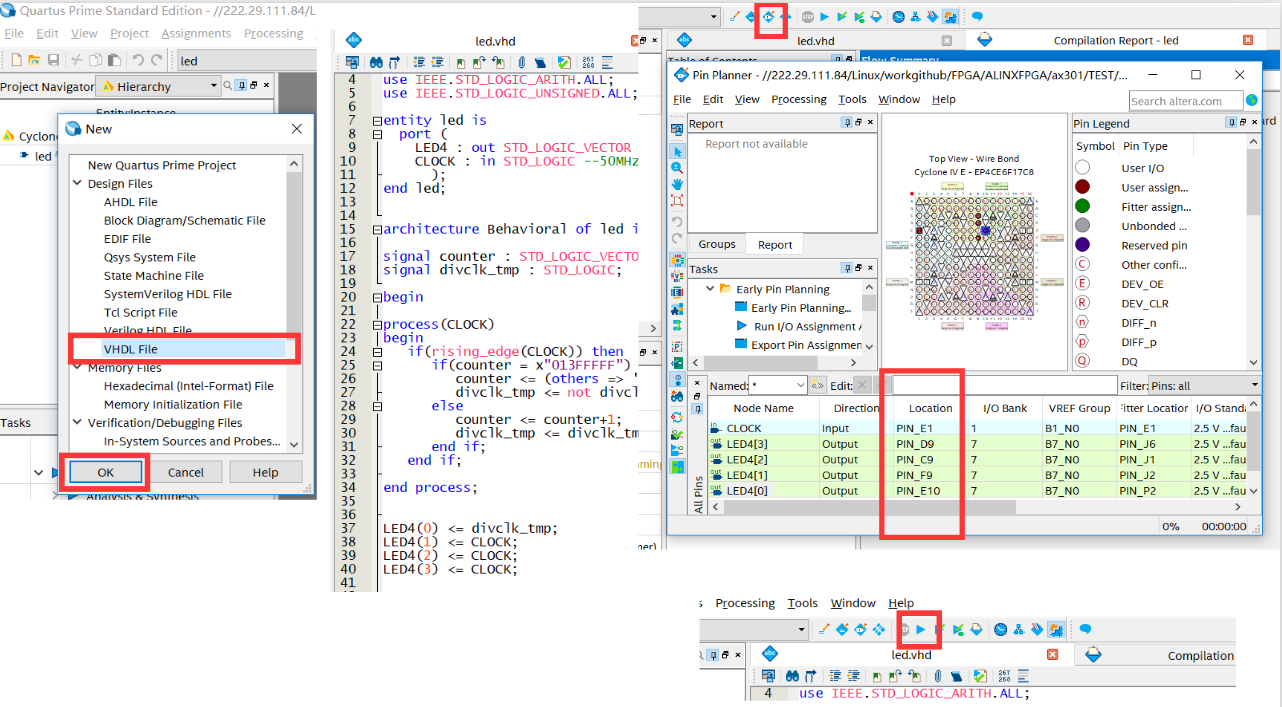

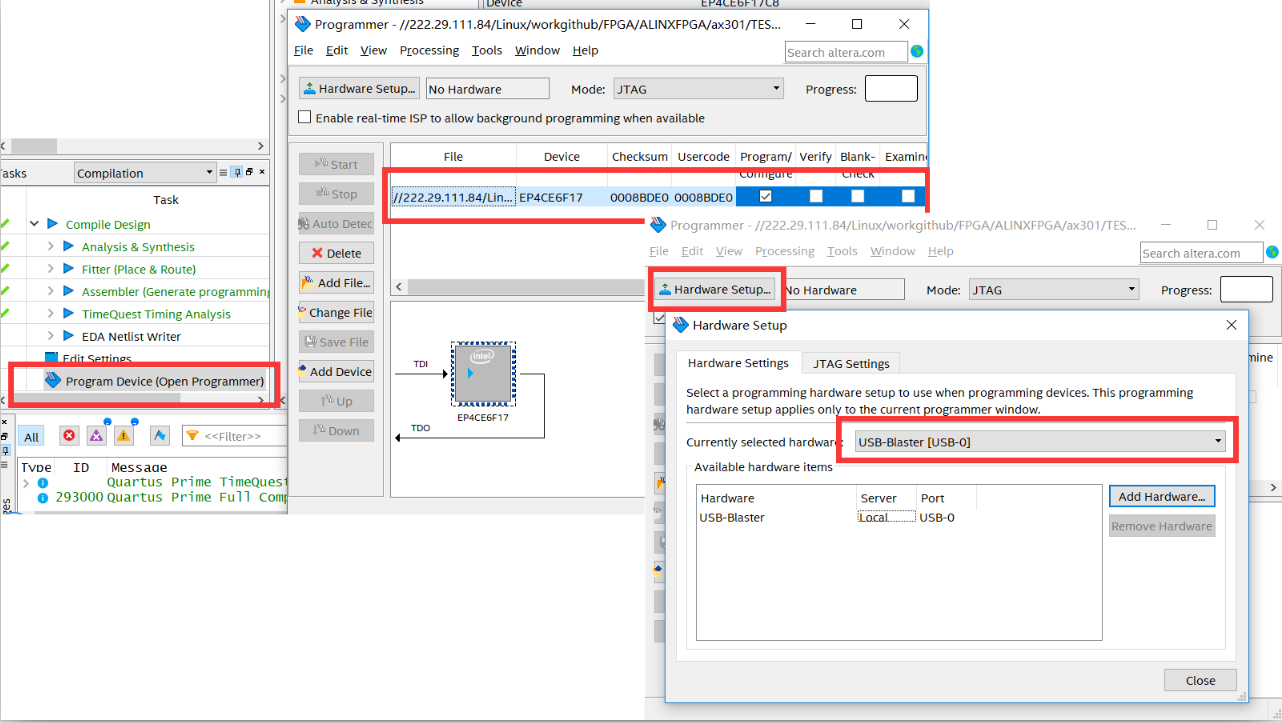

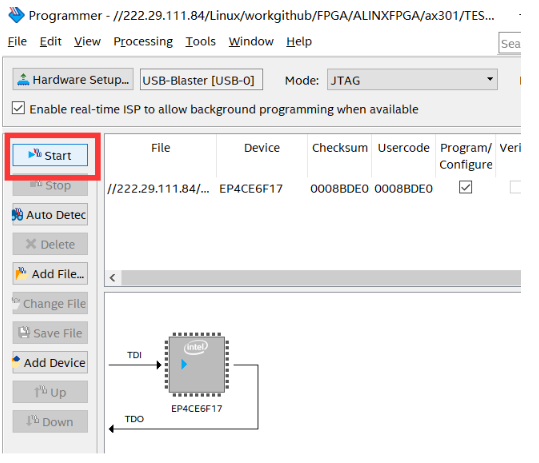

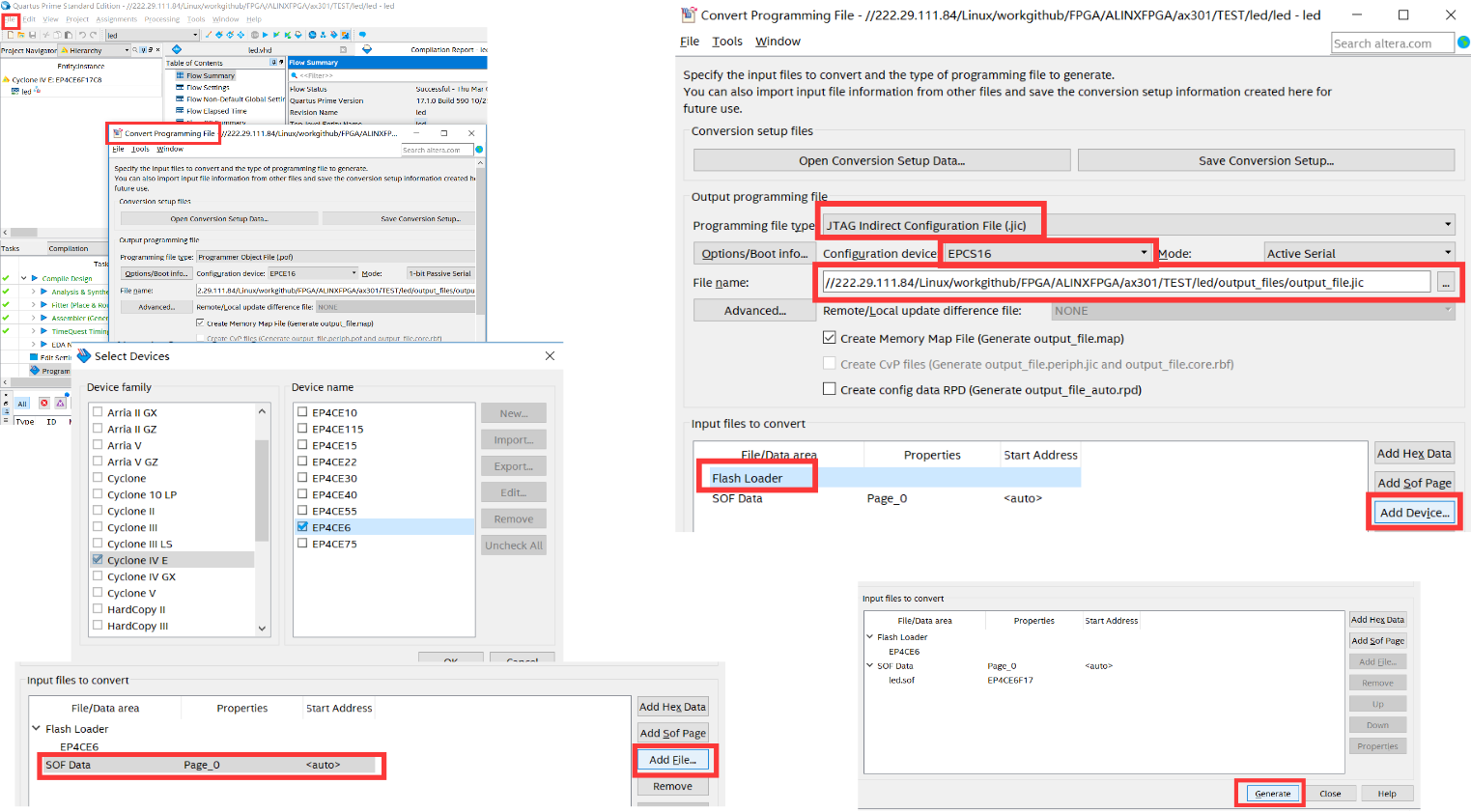

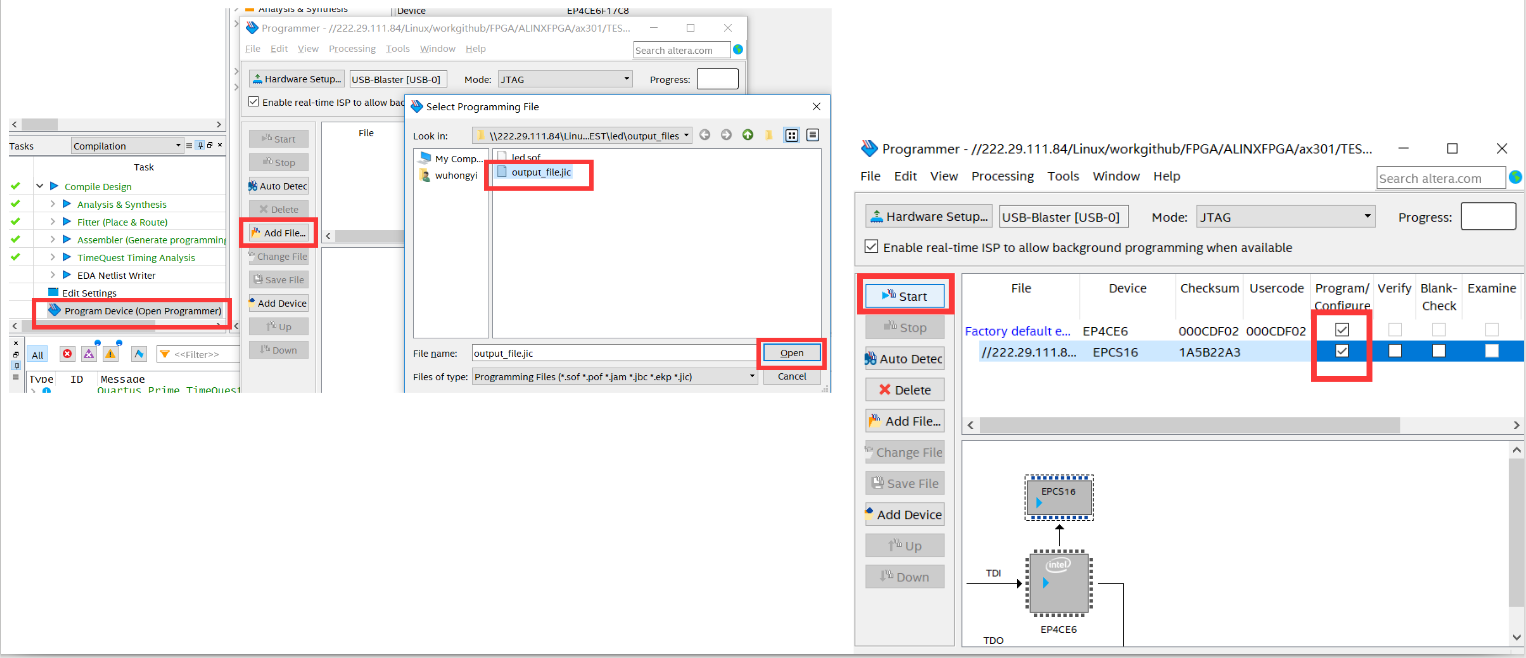

刷固件方式

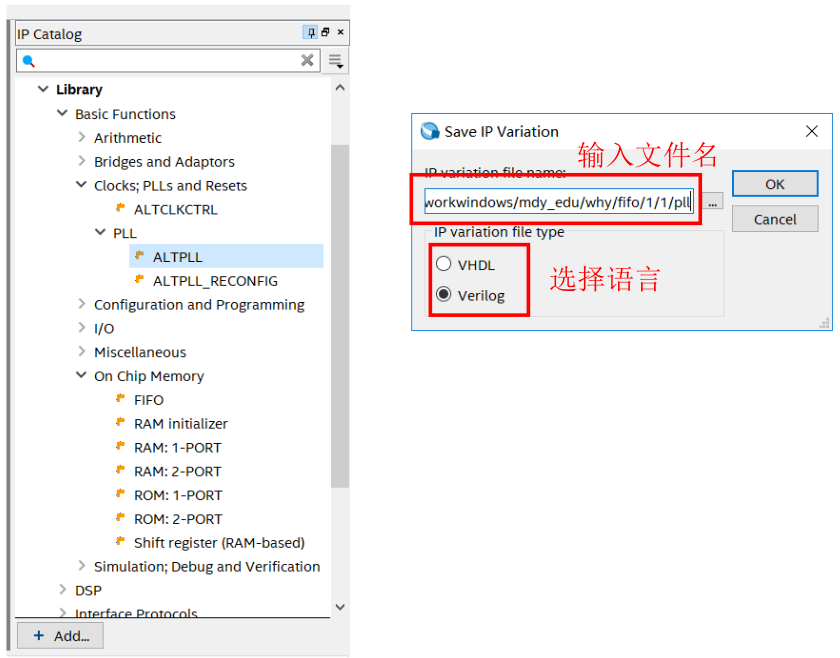

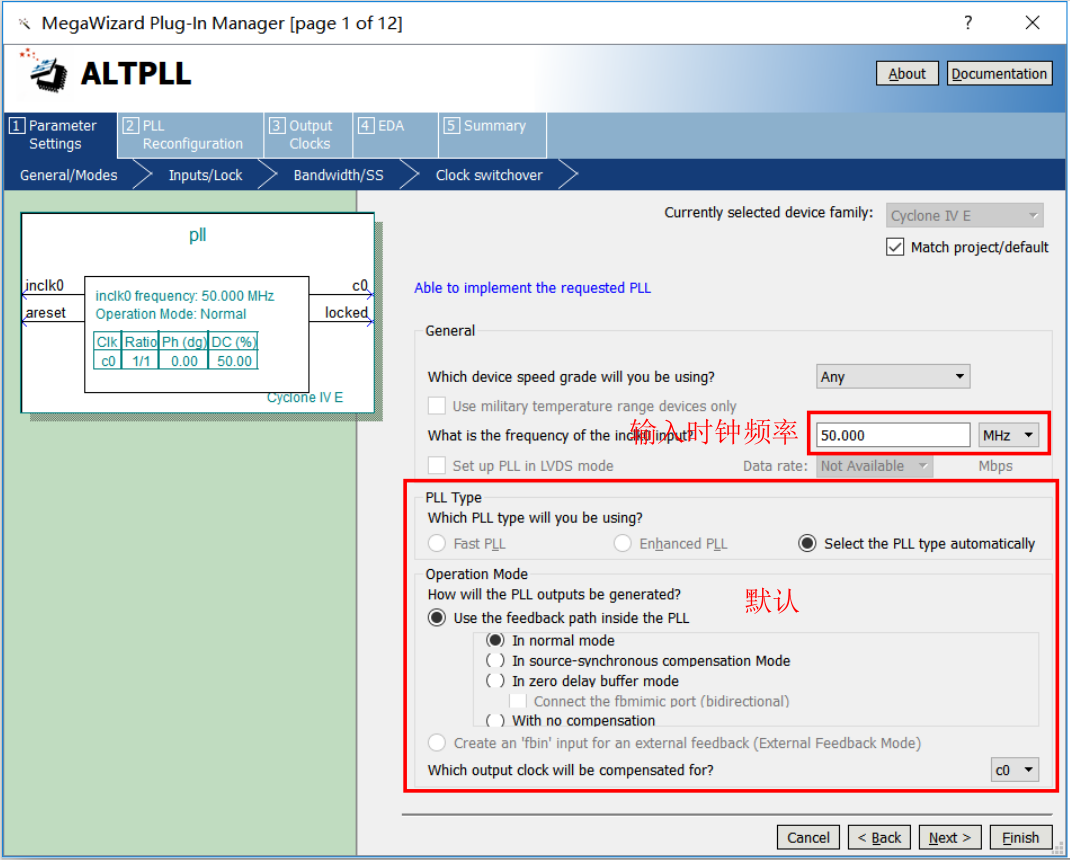

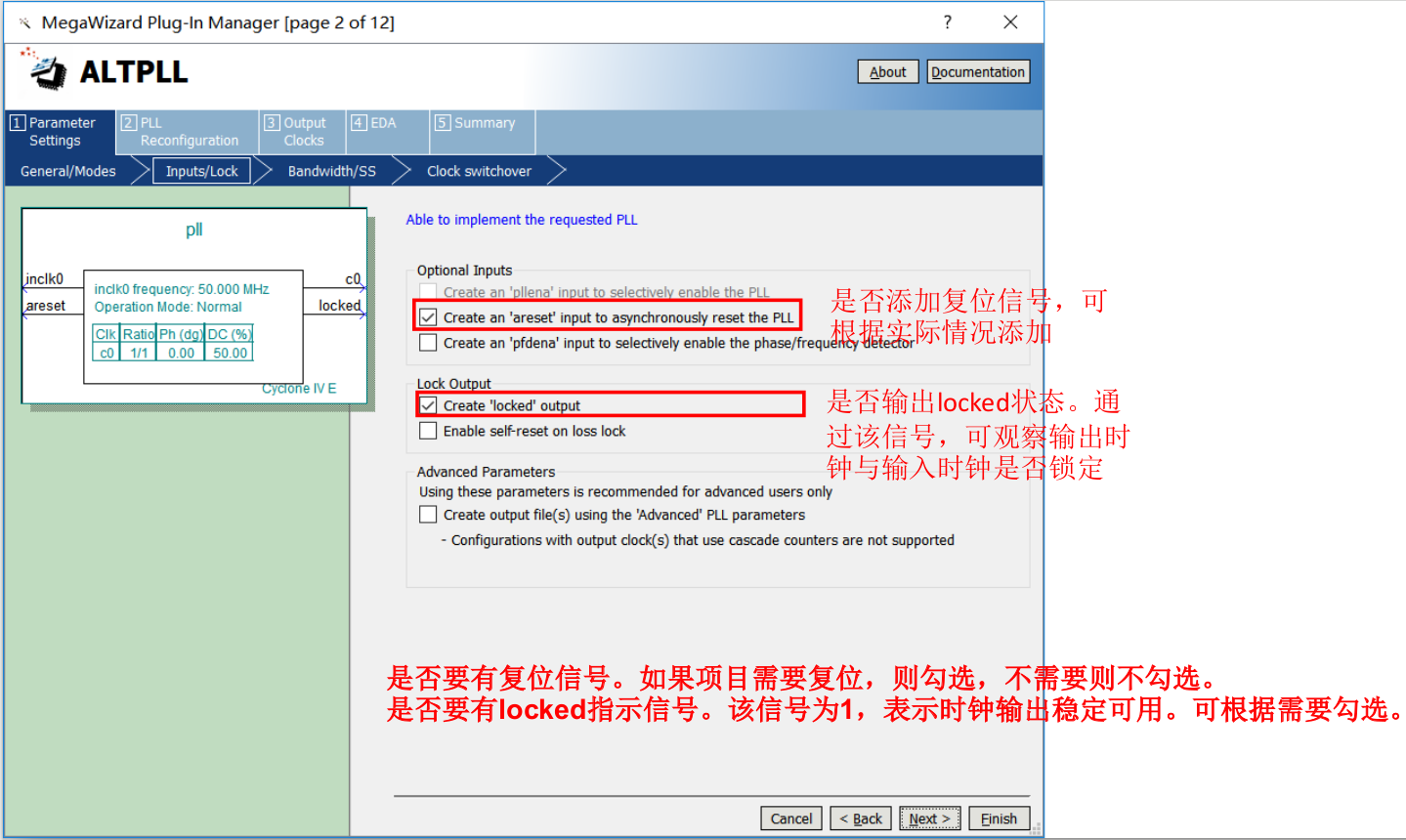

IP 核¶

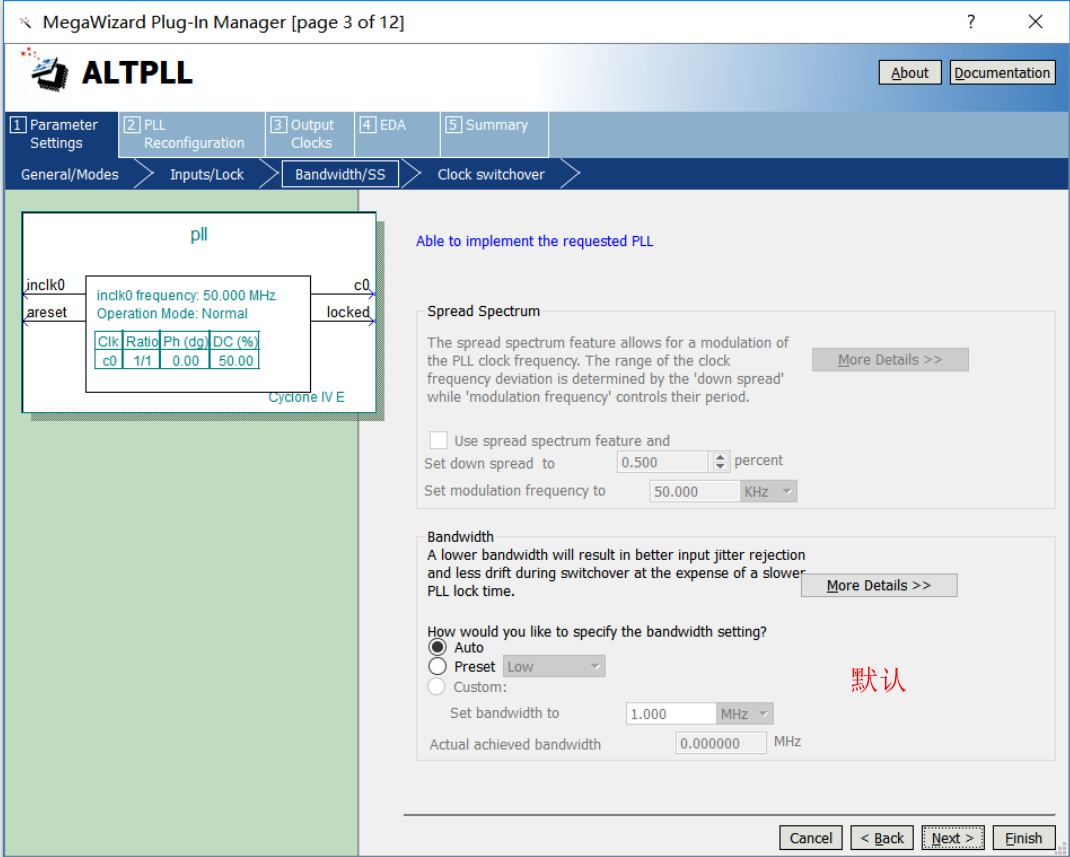

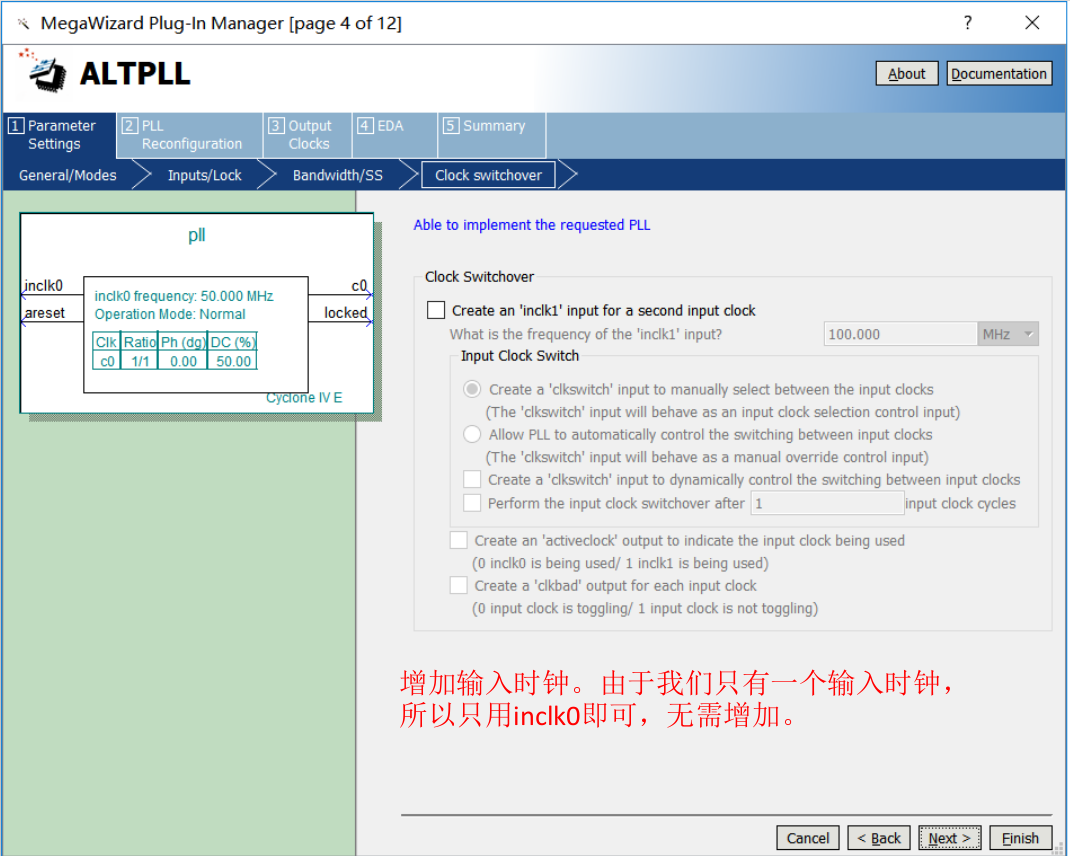

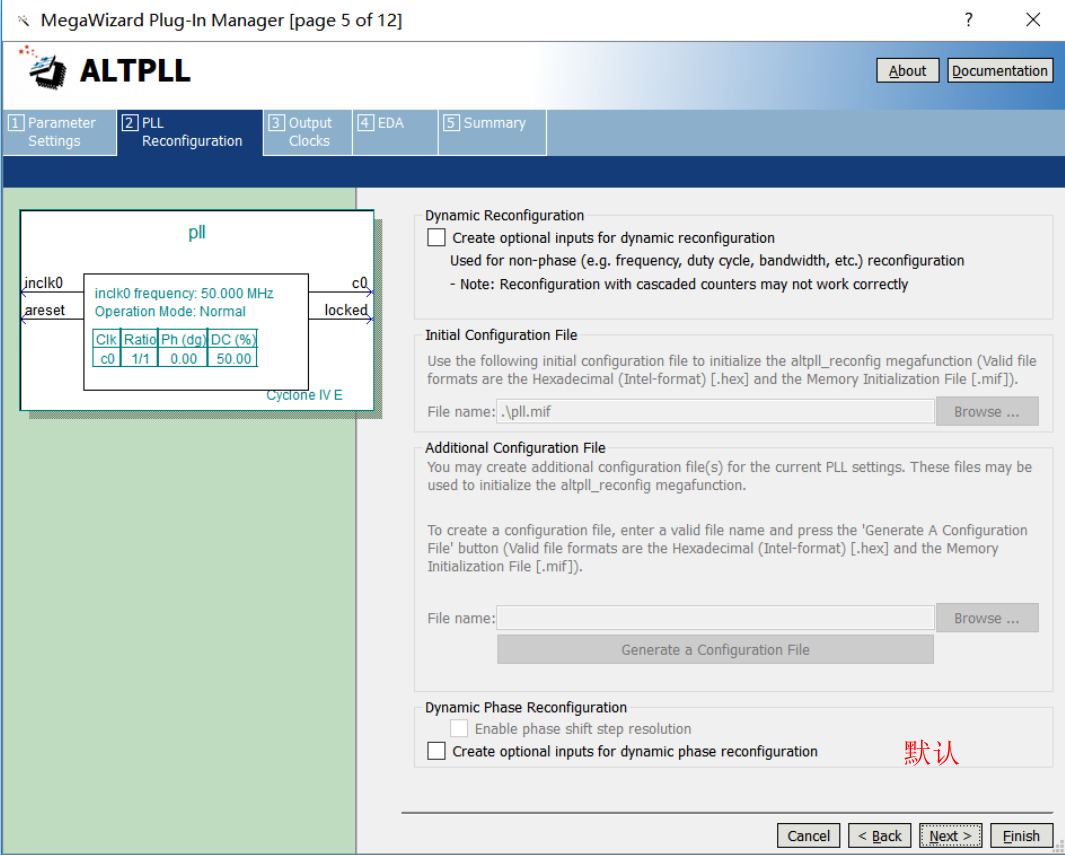

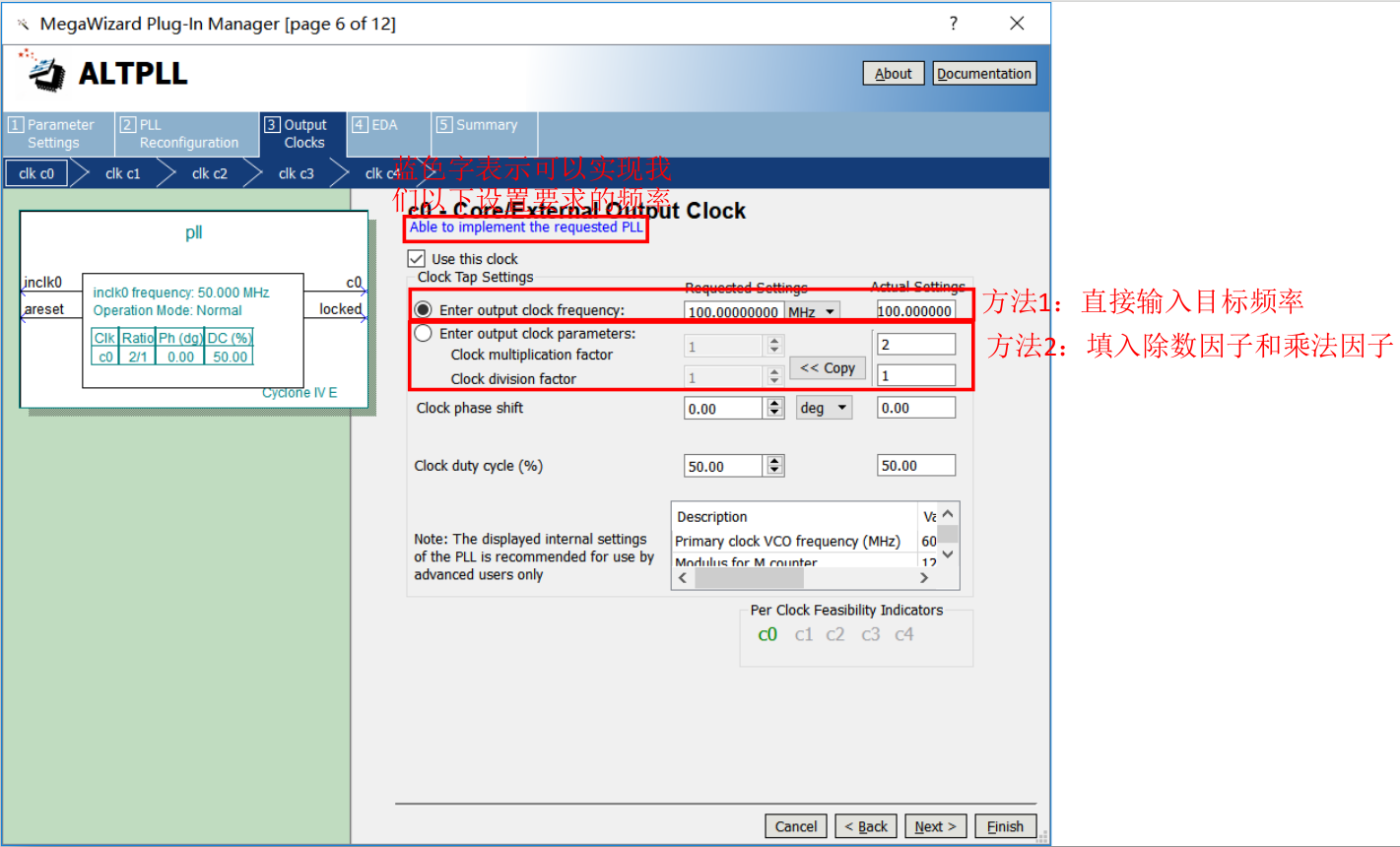

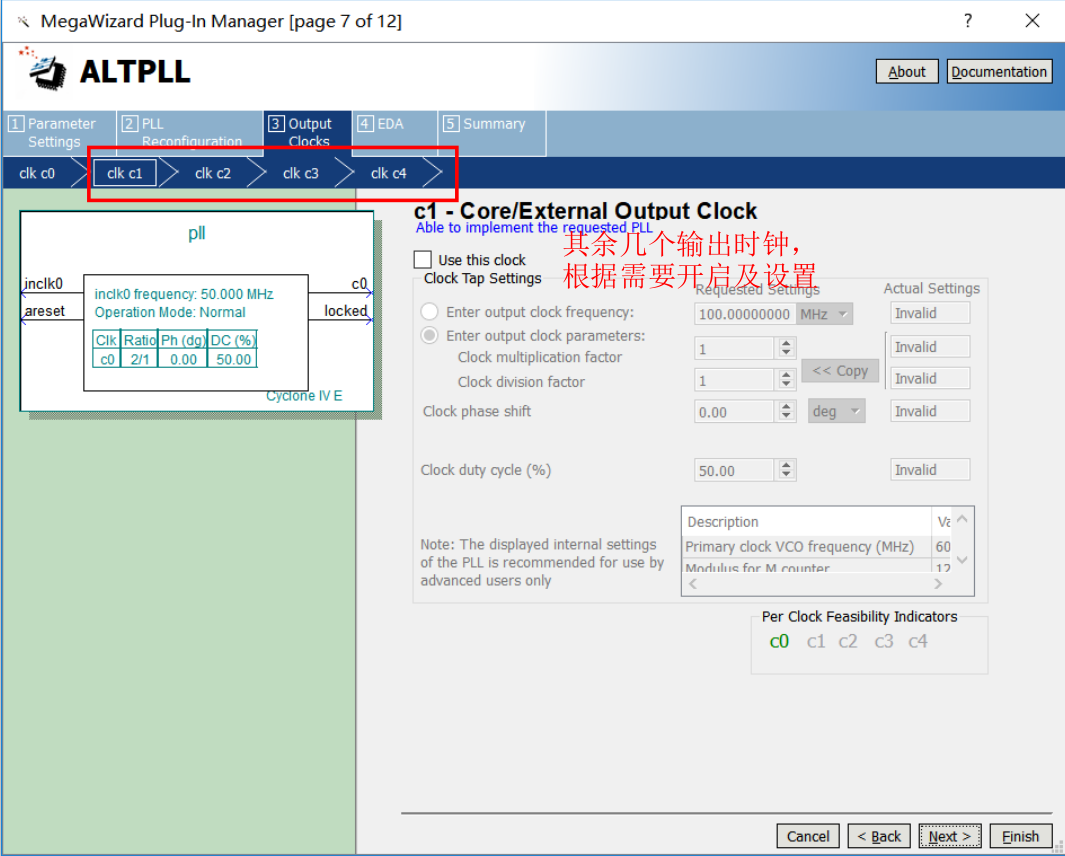

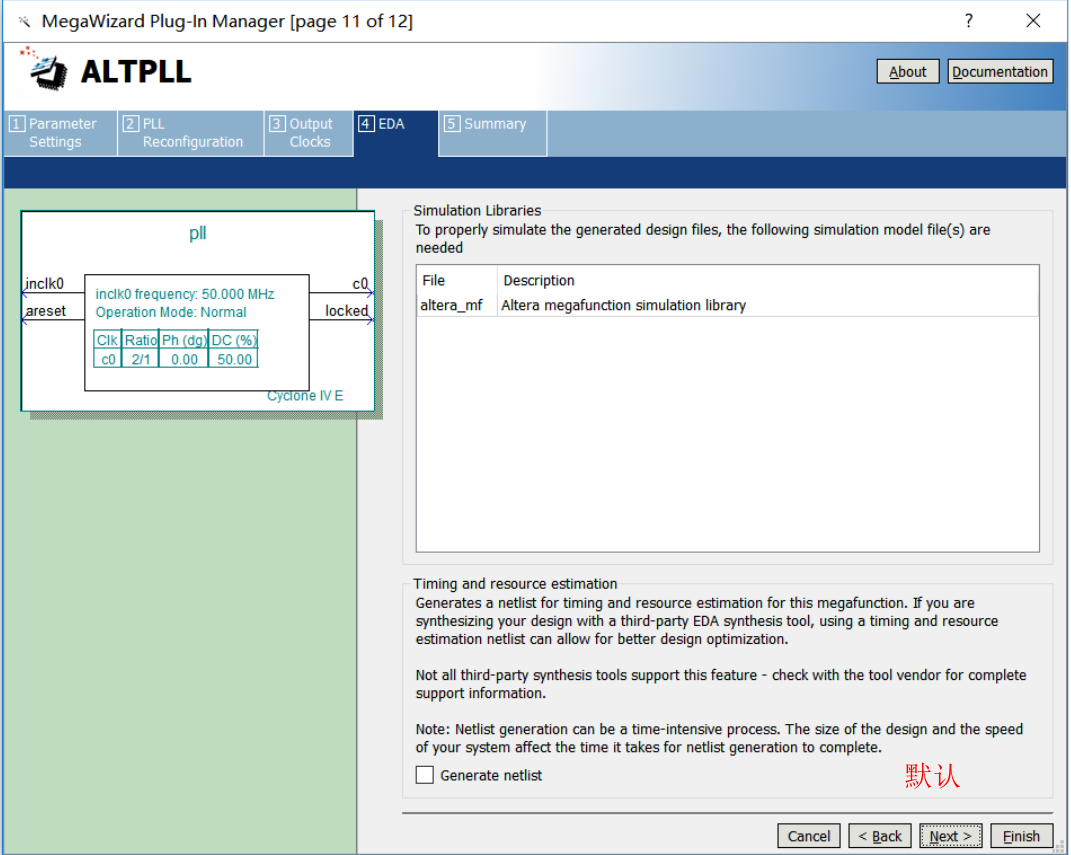

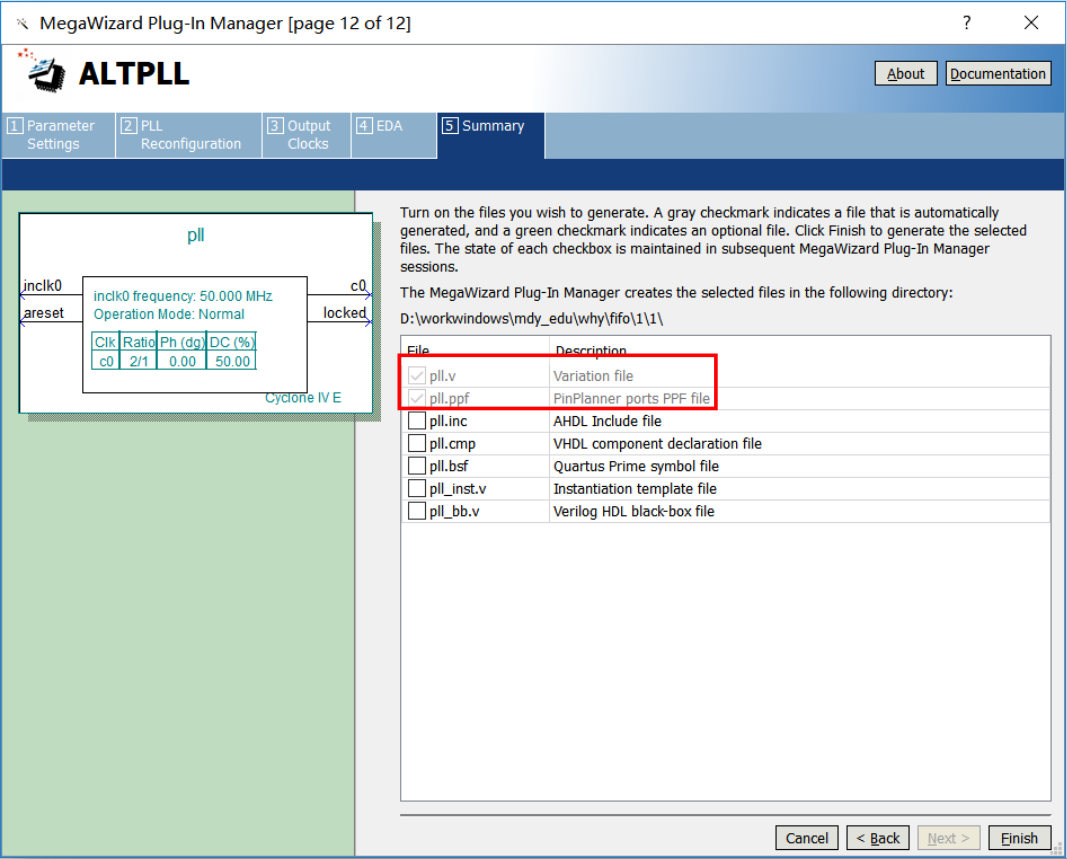

PLL

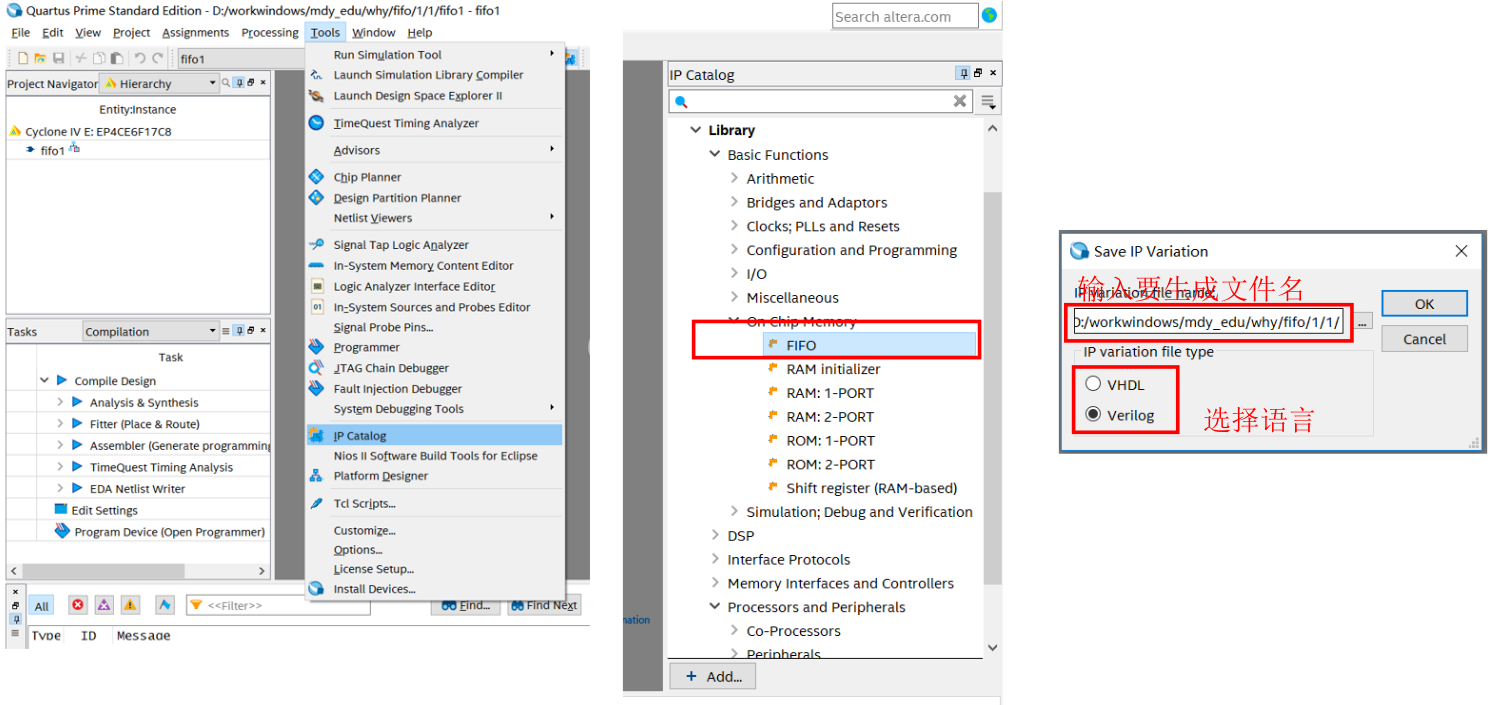

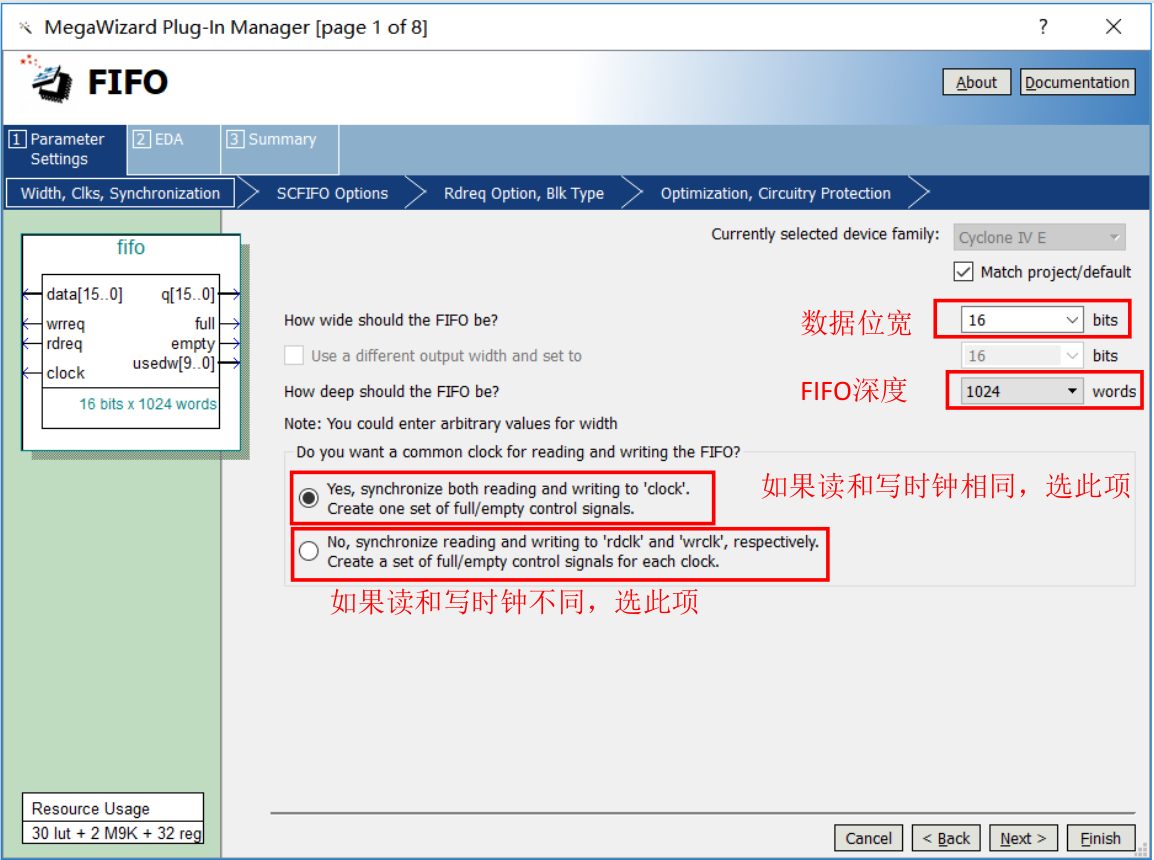

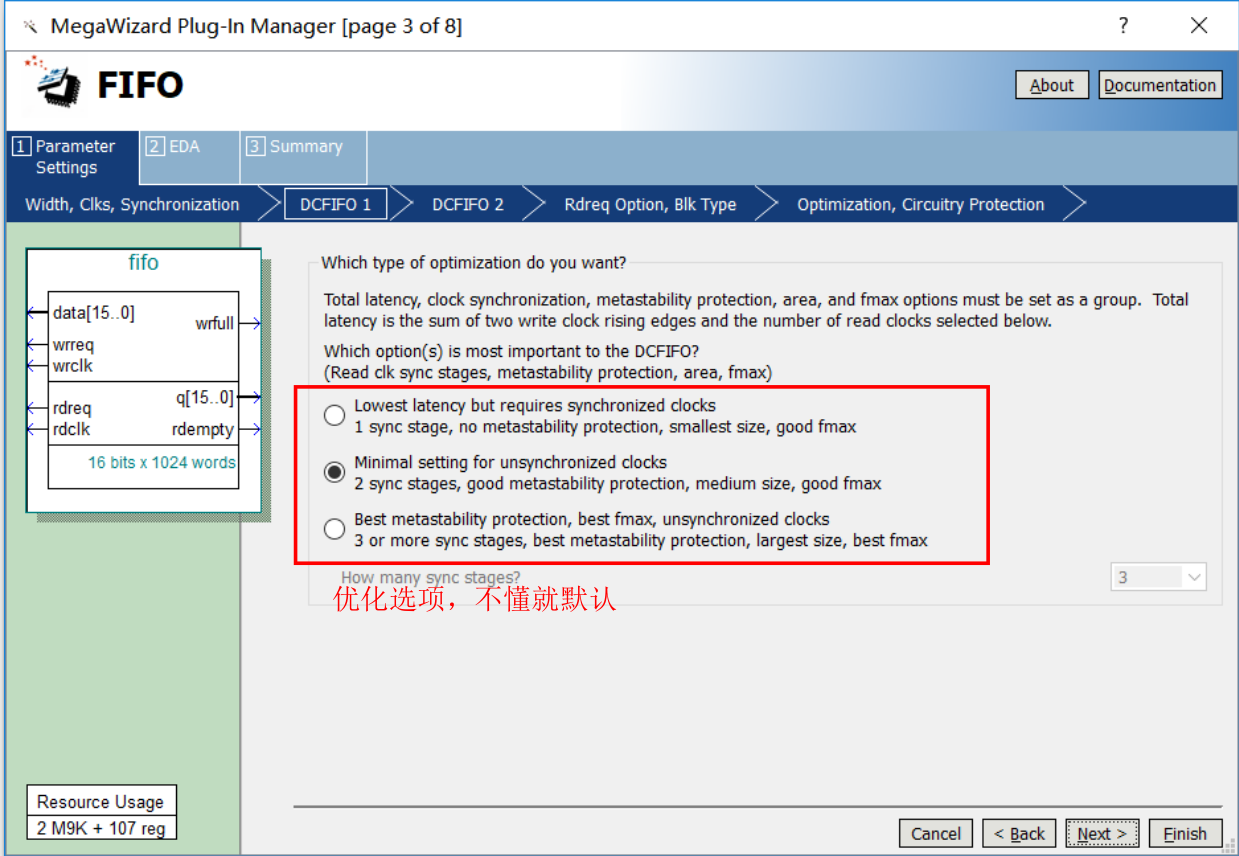

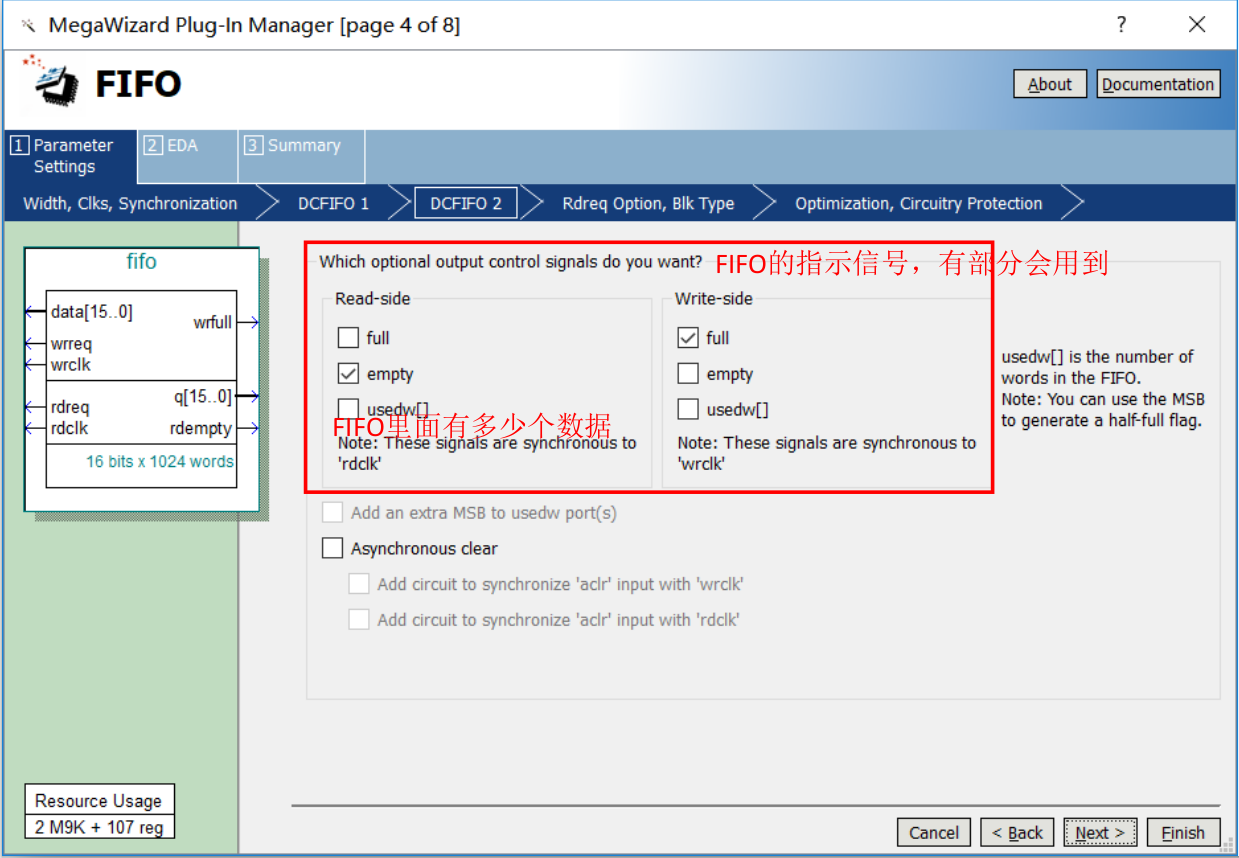

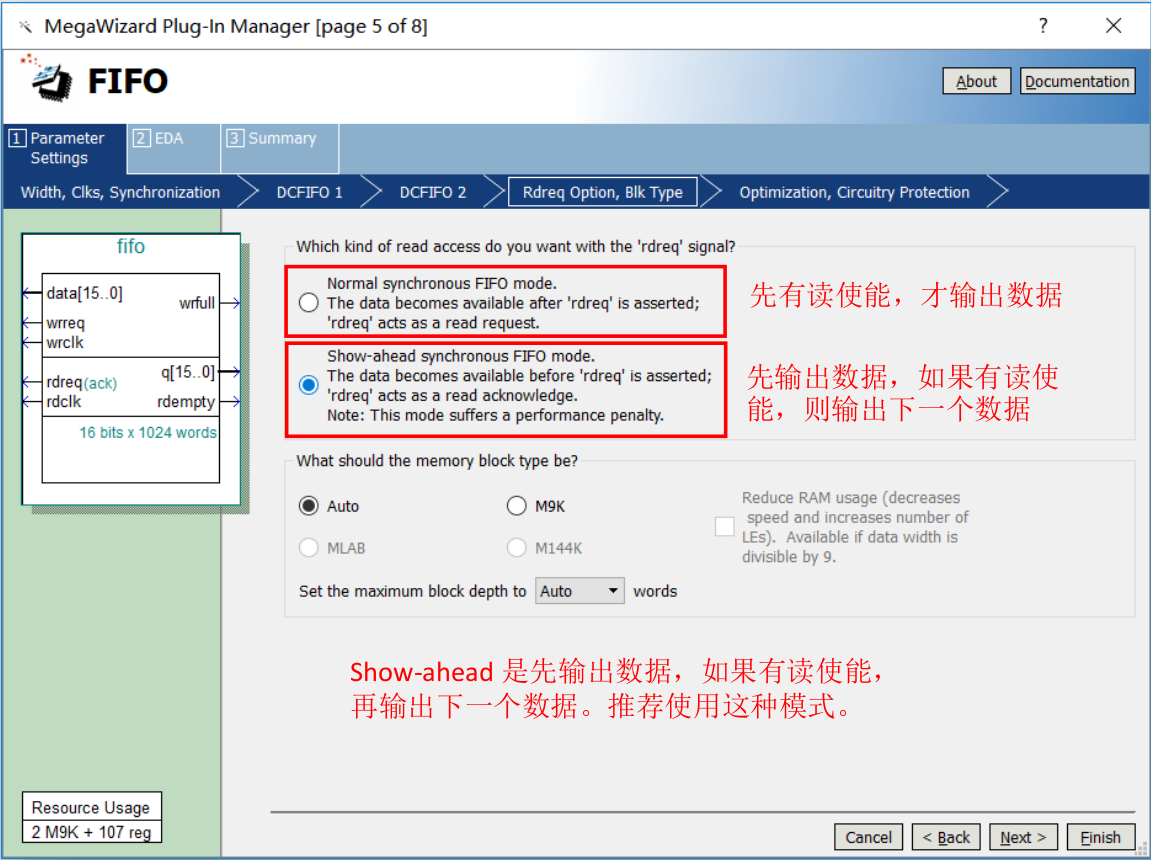

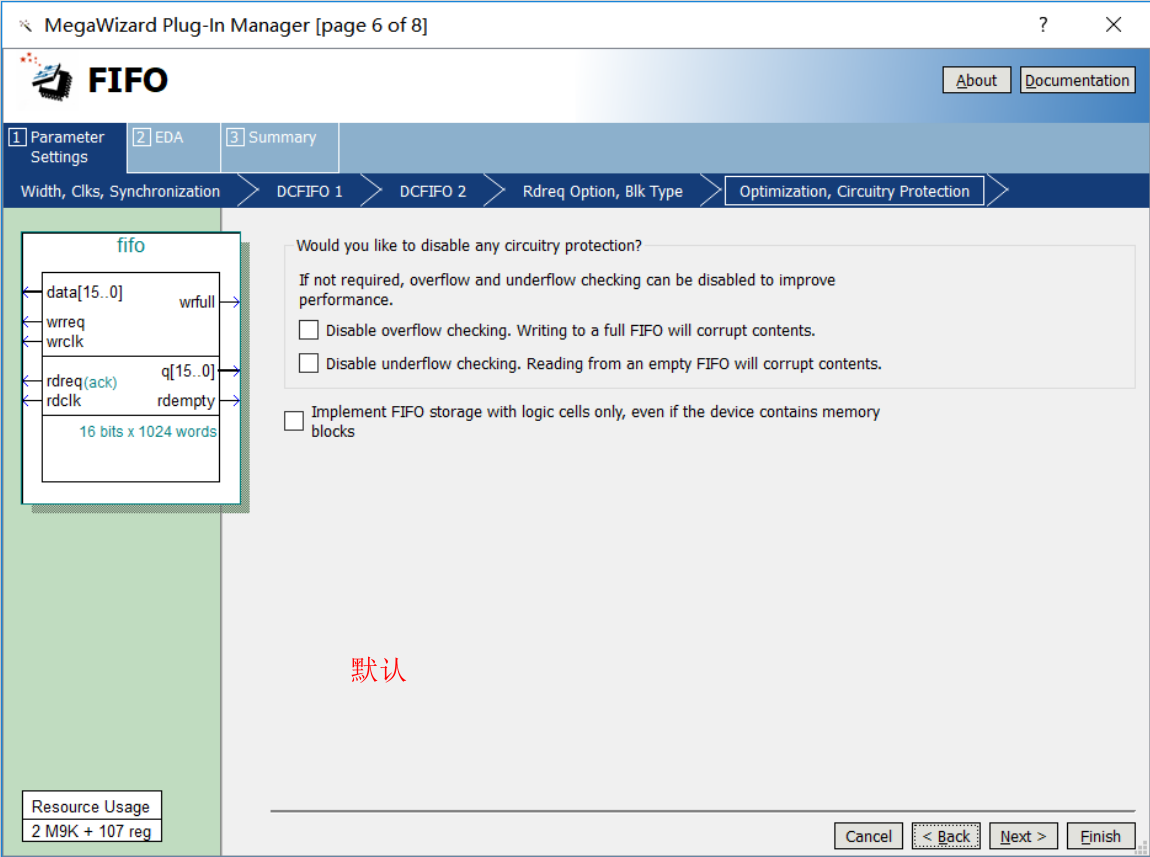

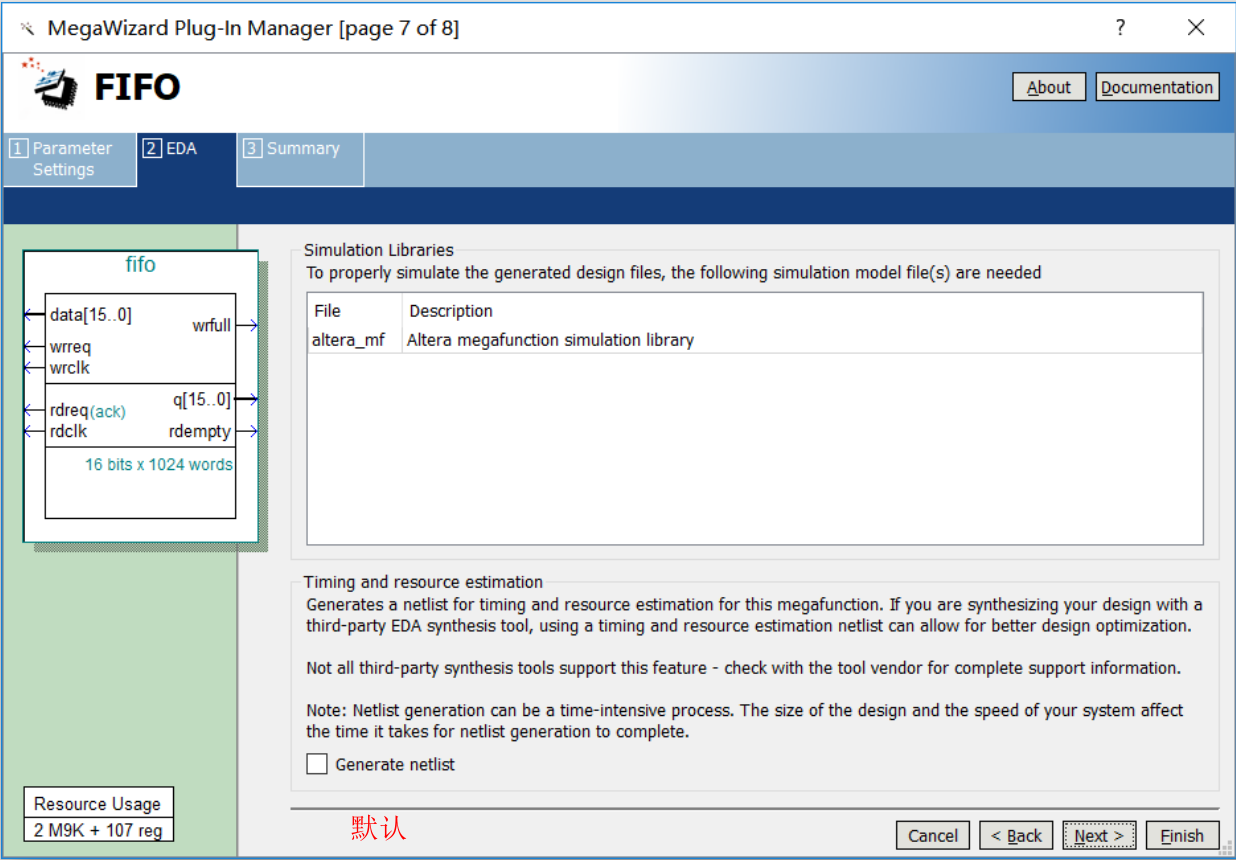

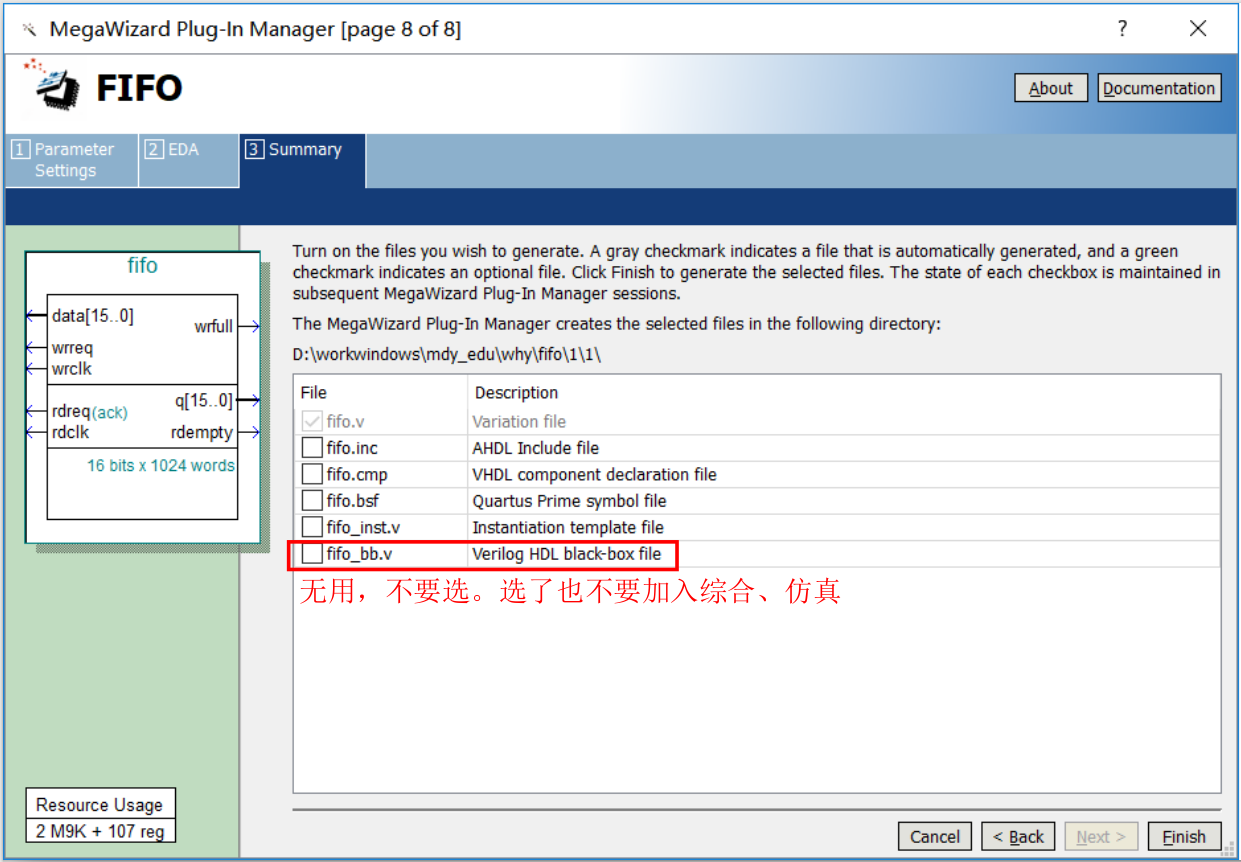

FIFO

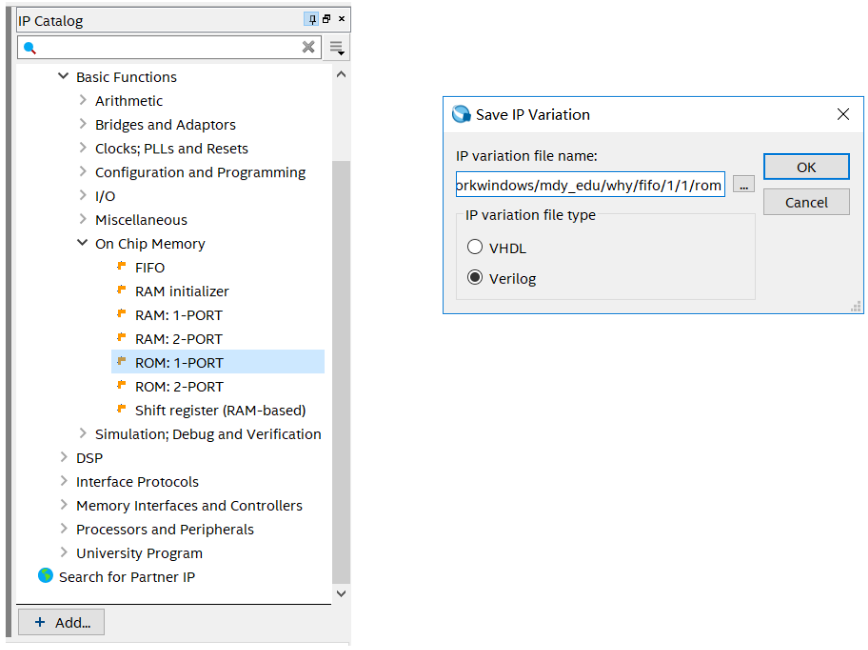

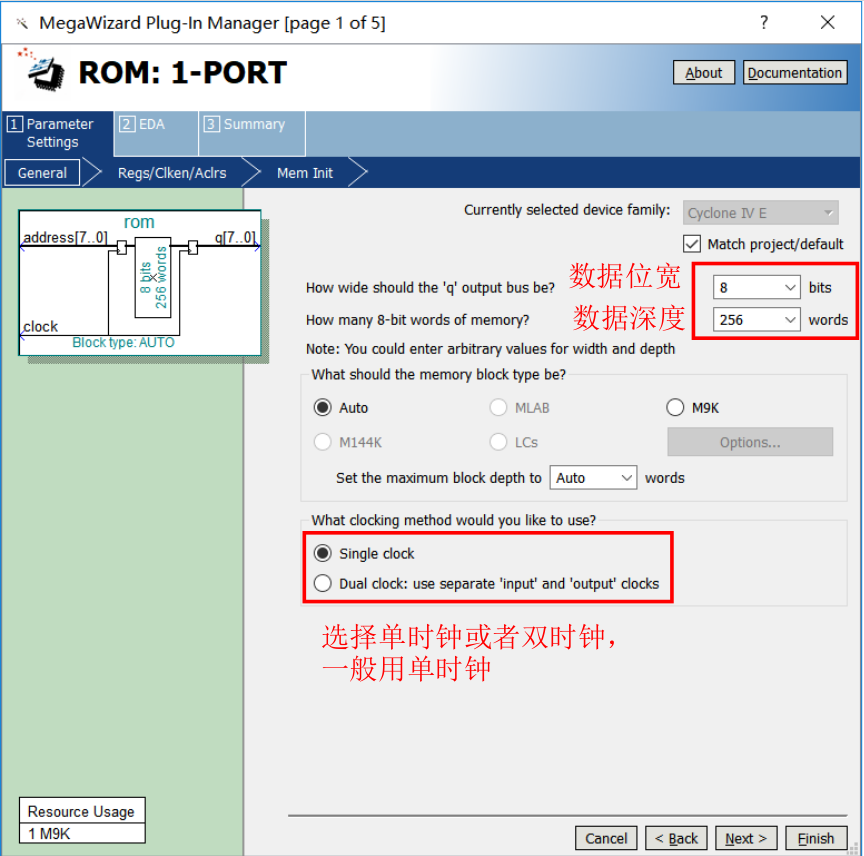

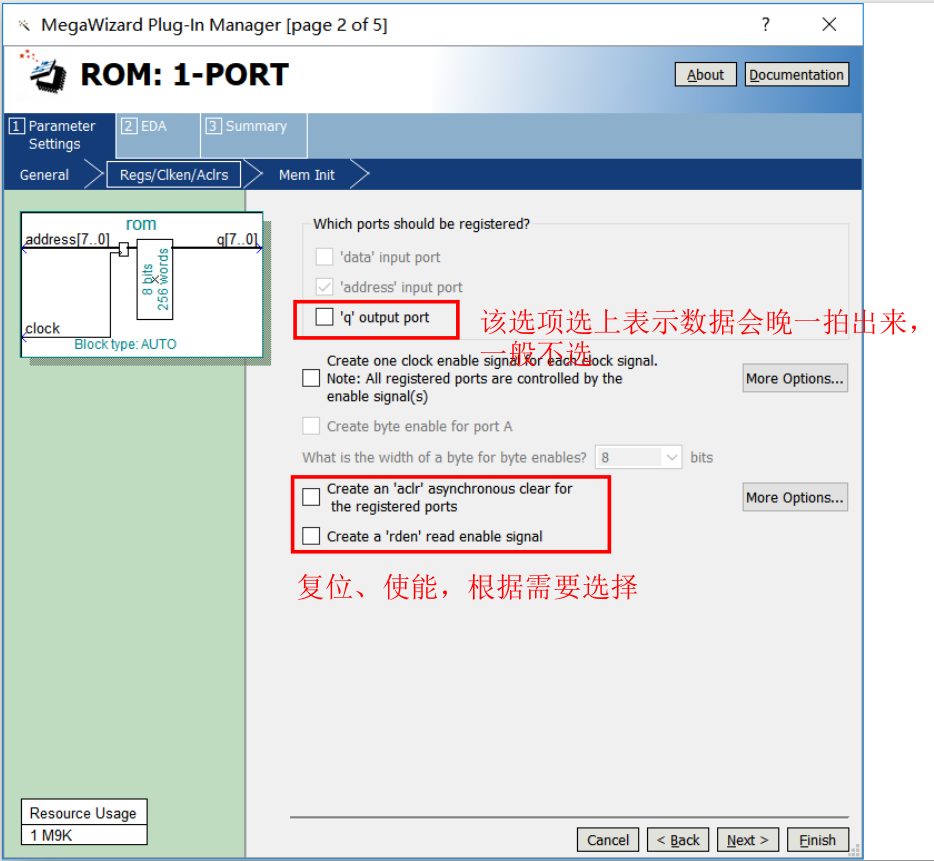

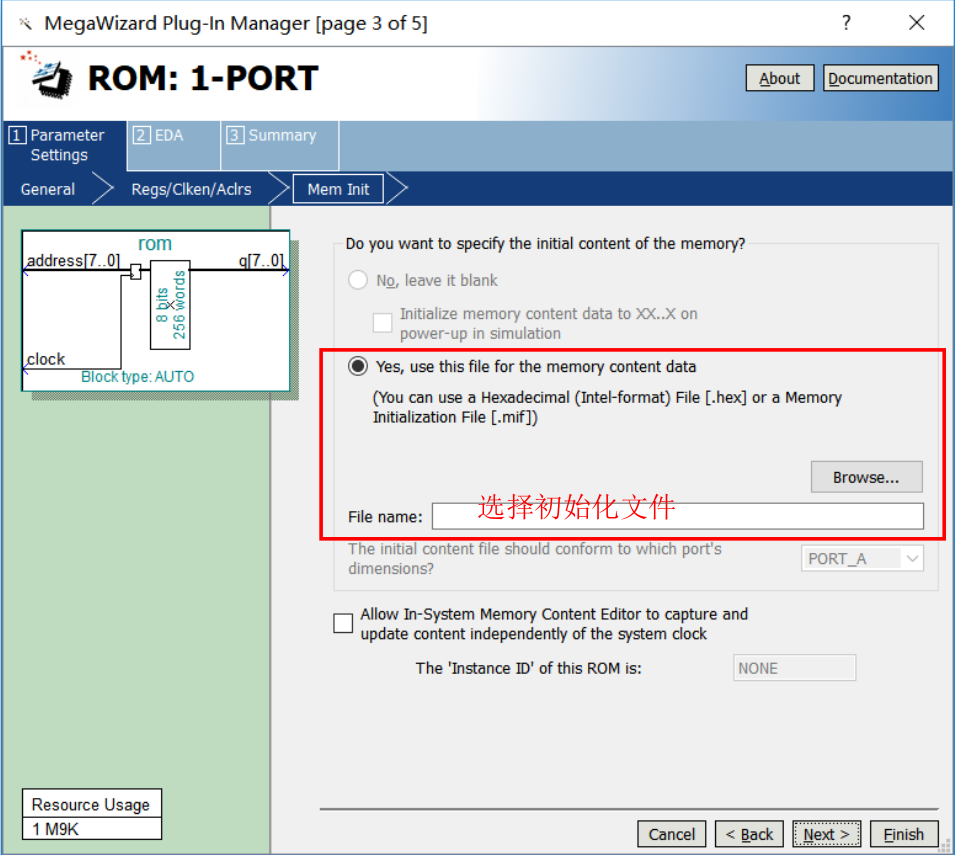

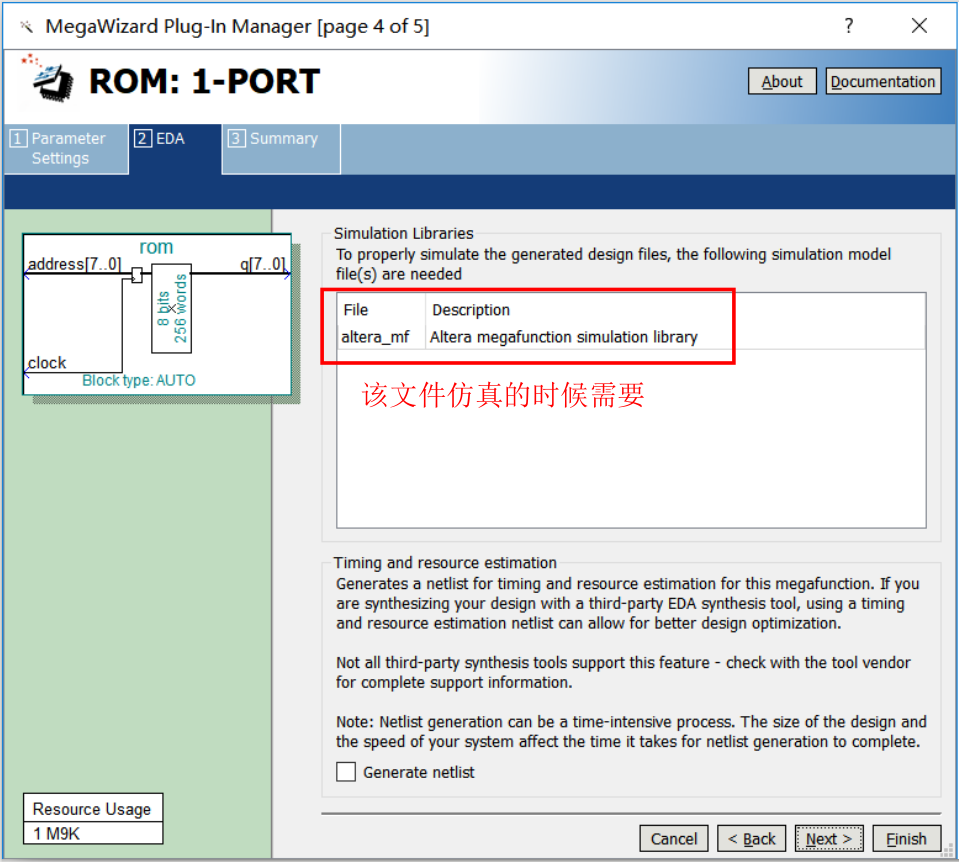

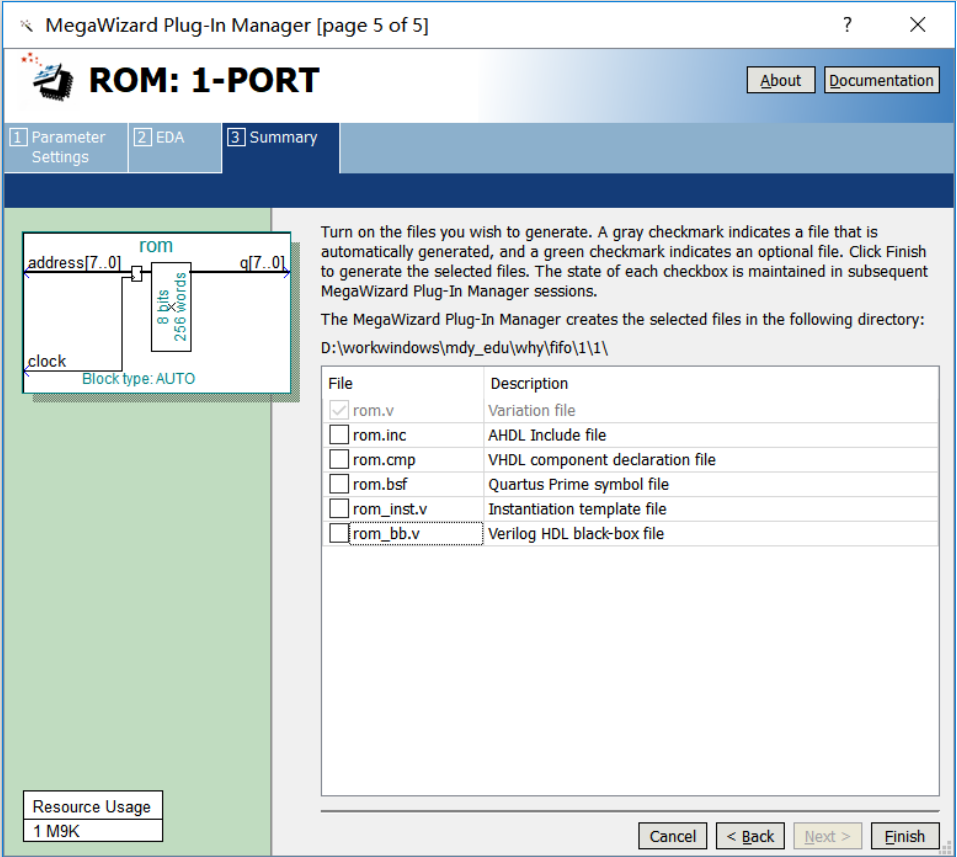

RAMROM

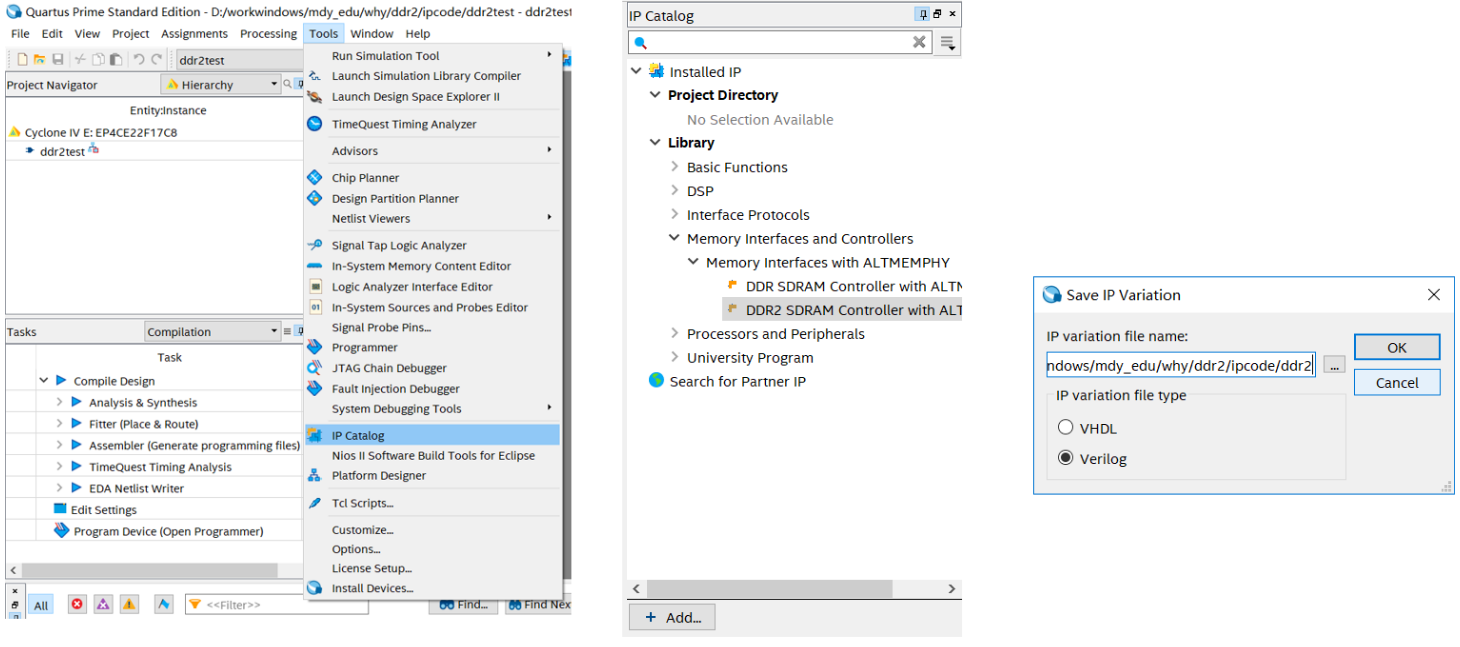

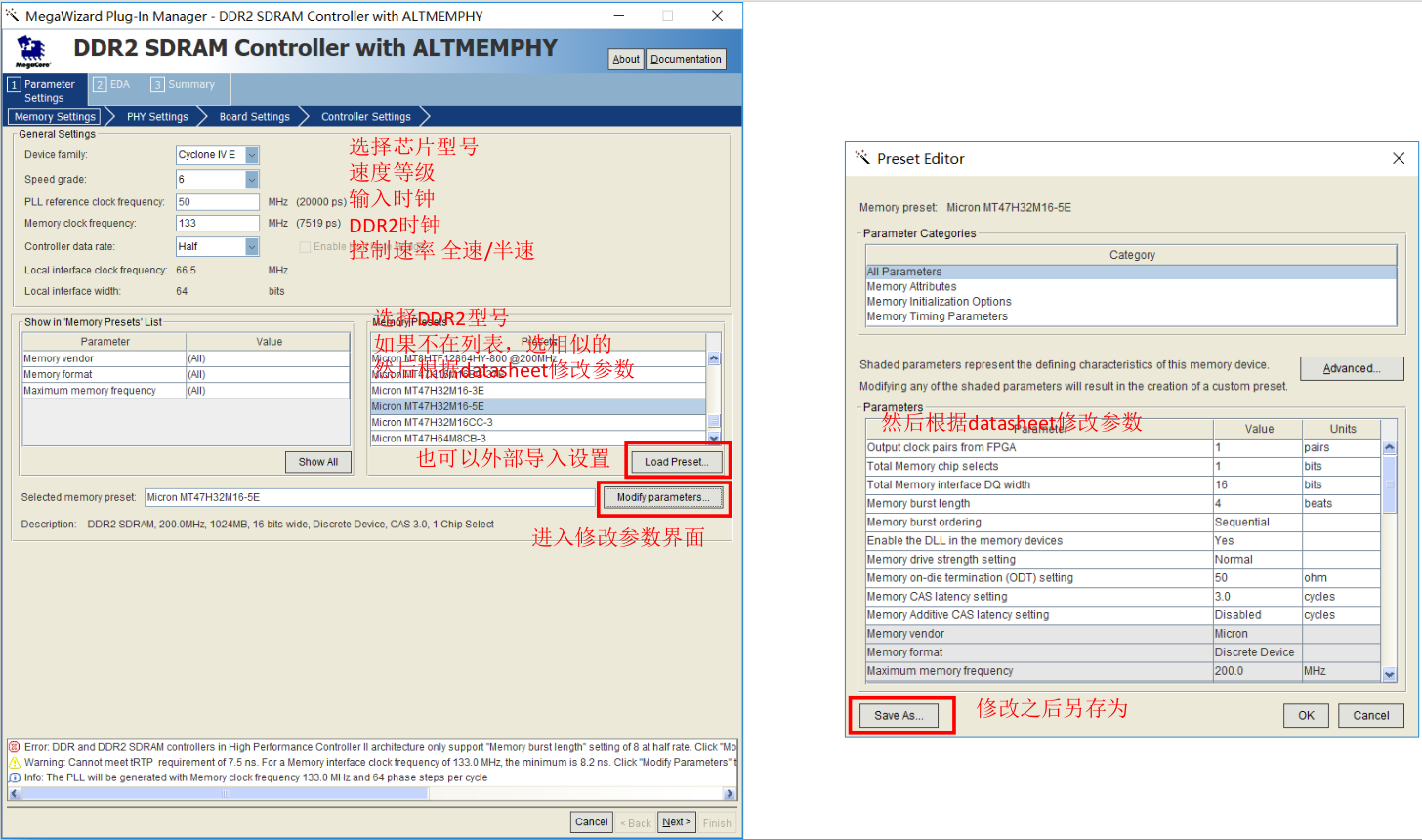

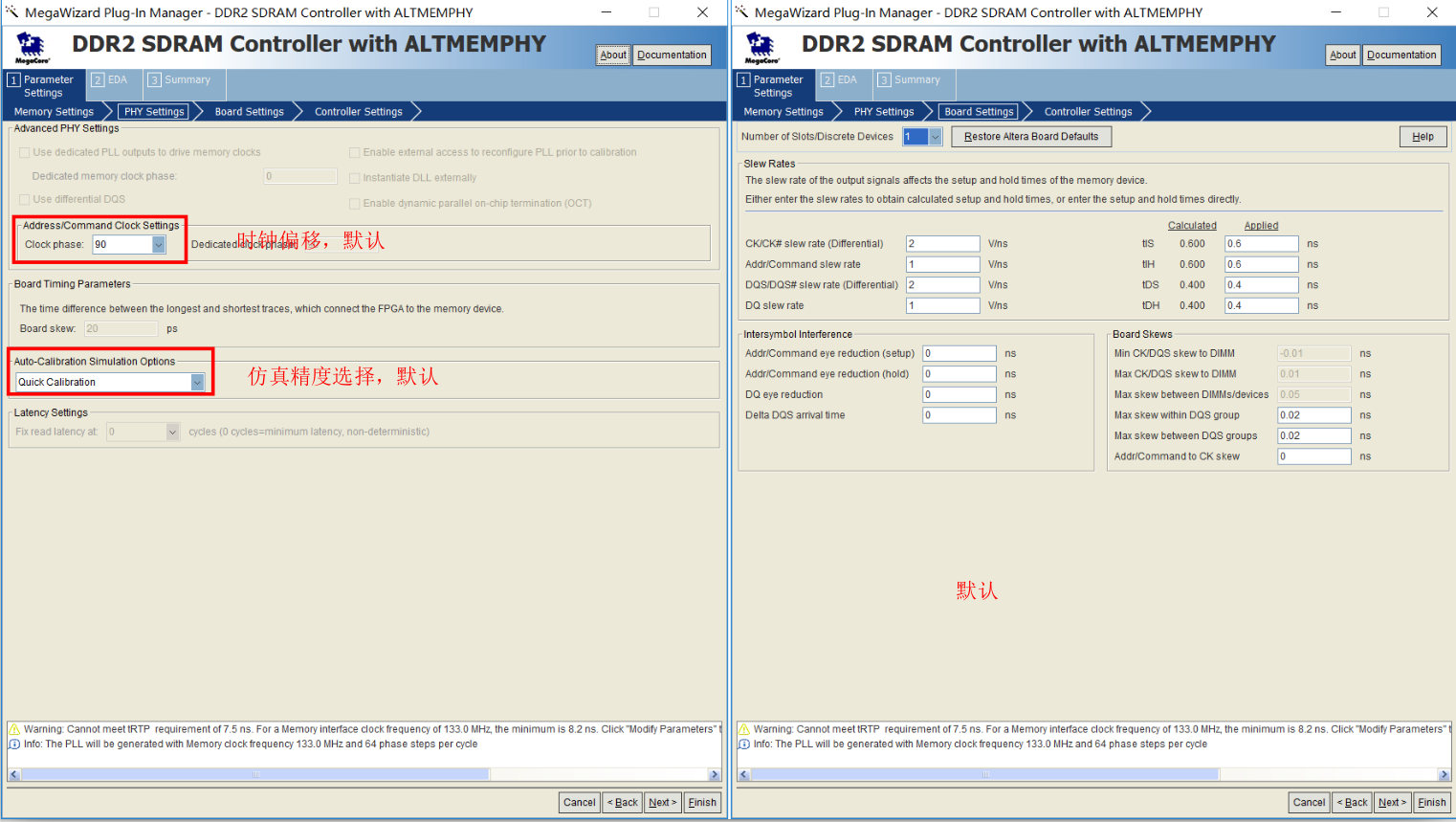

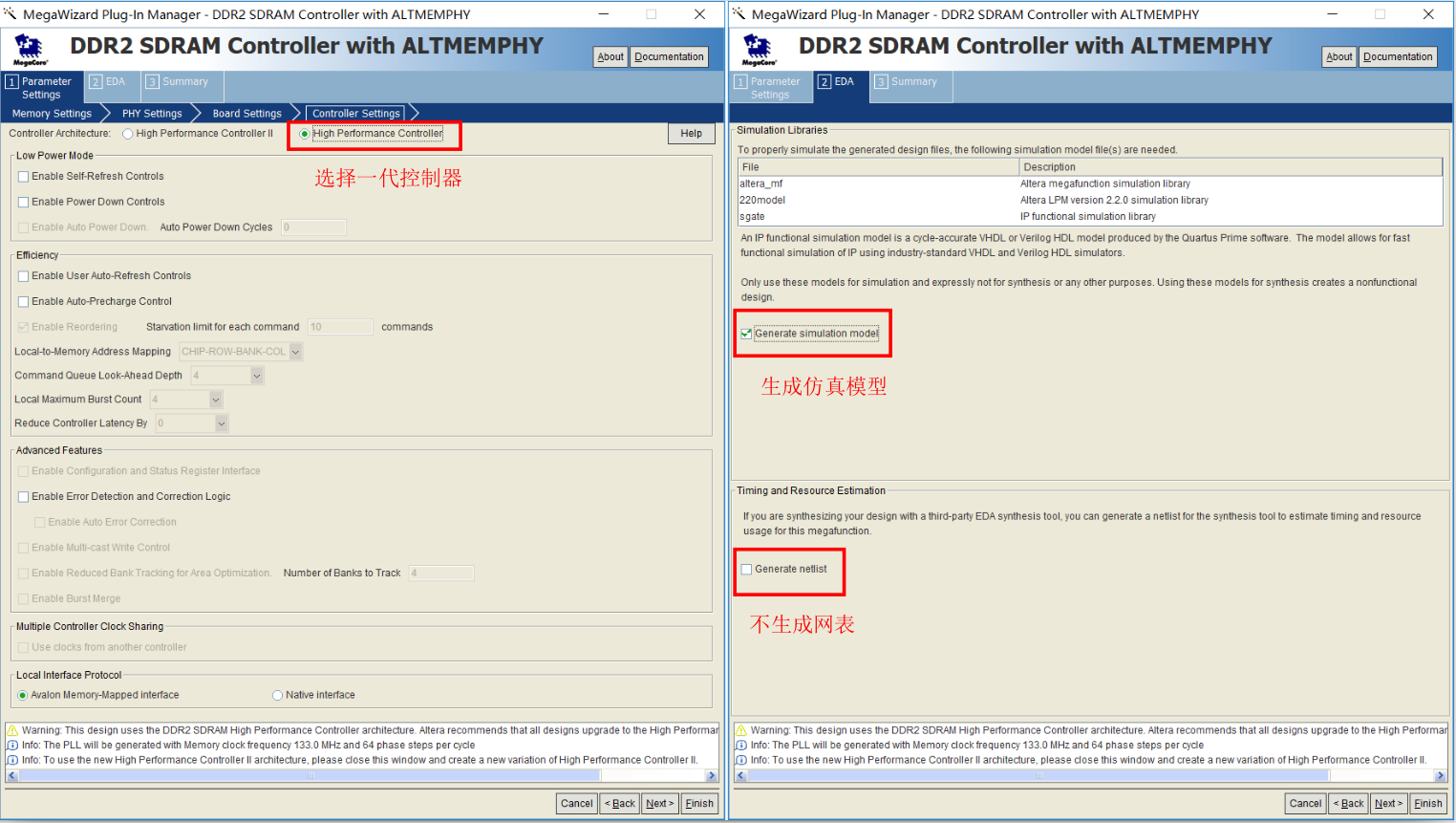

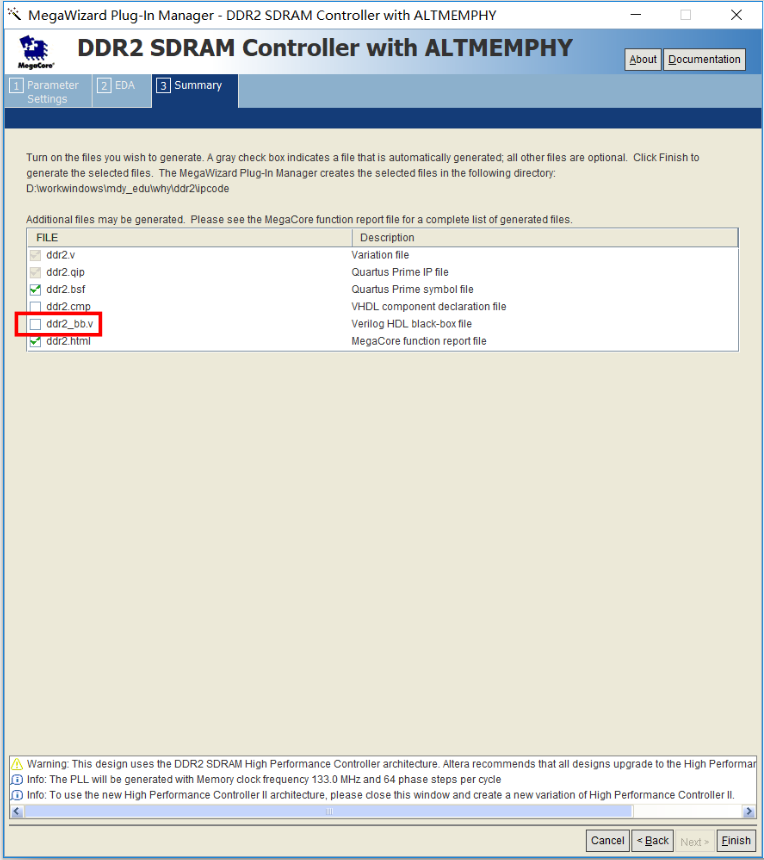

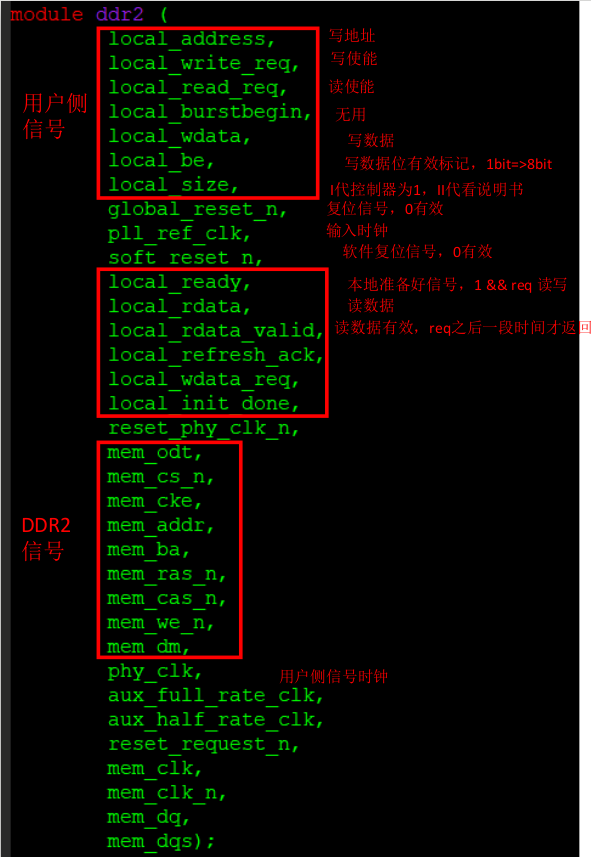

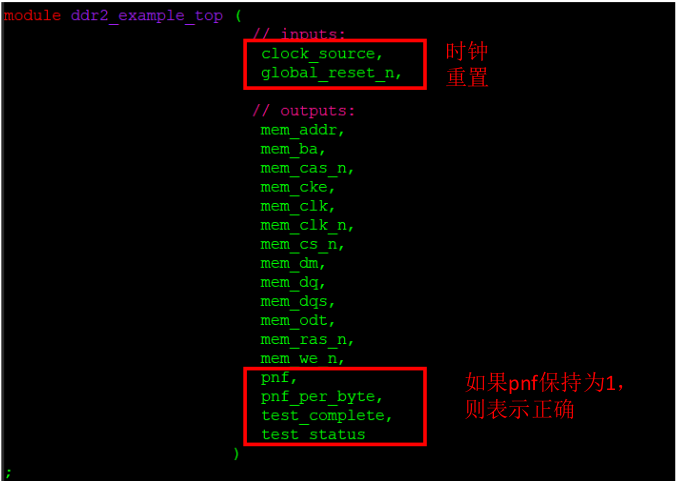

DDRSDRAM

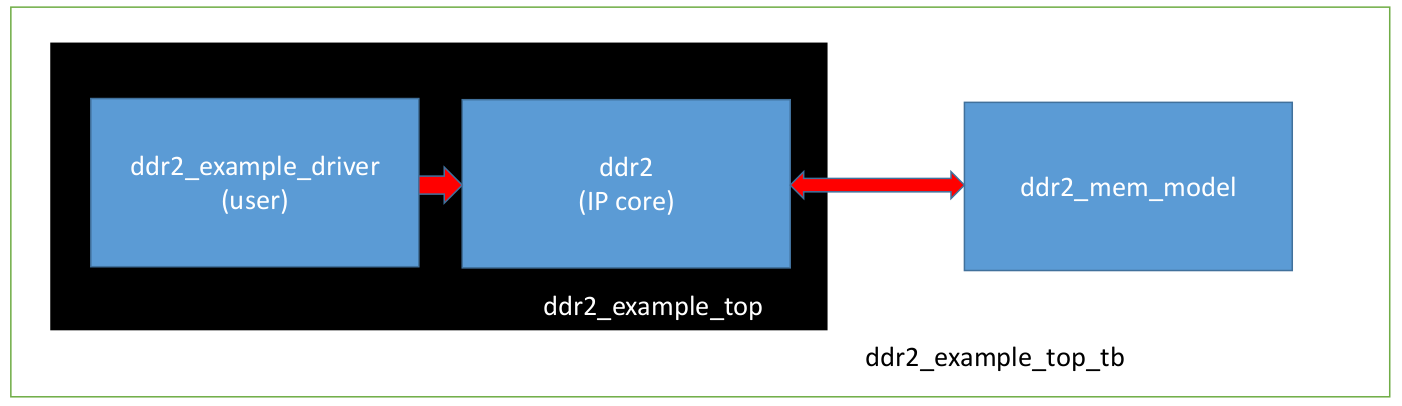

IP 核生成后会有一个测试用的顶层文件,该文件可以用来测试硬件是否有问题

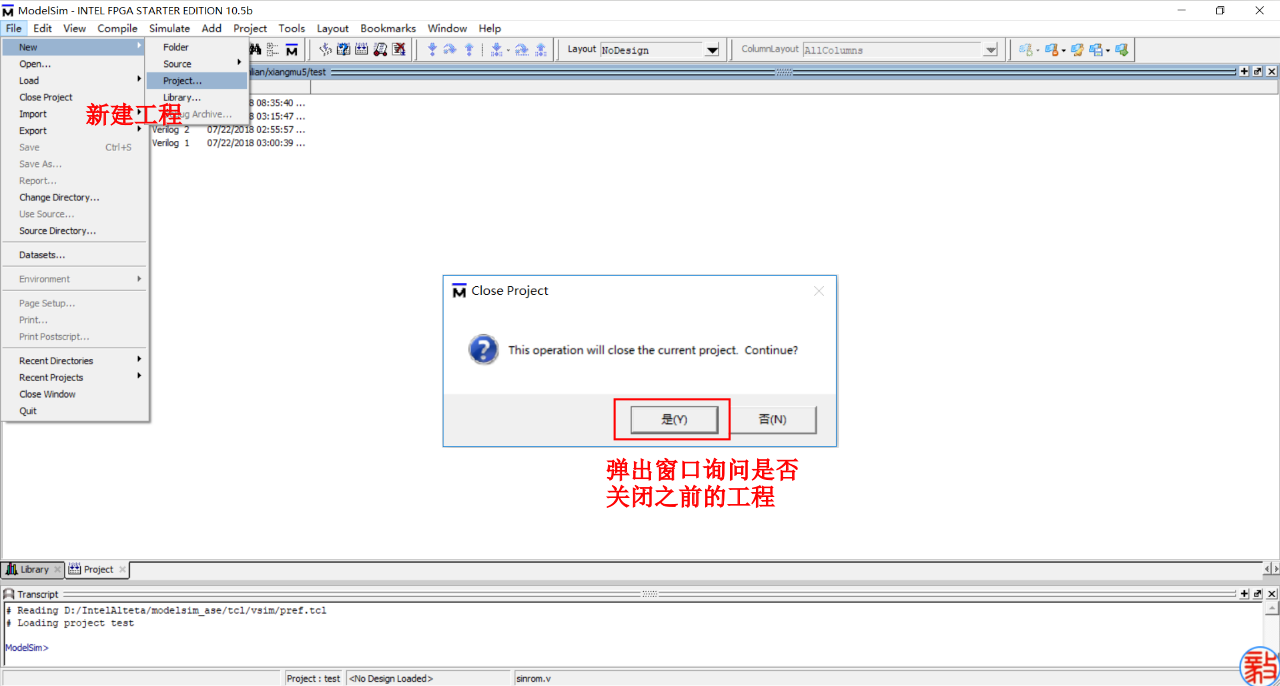

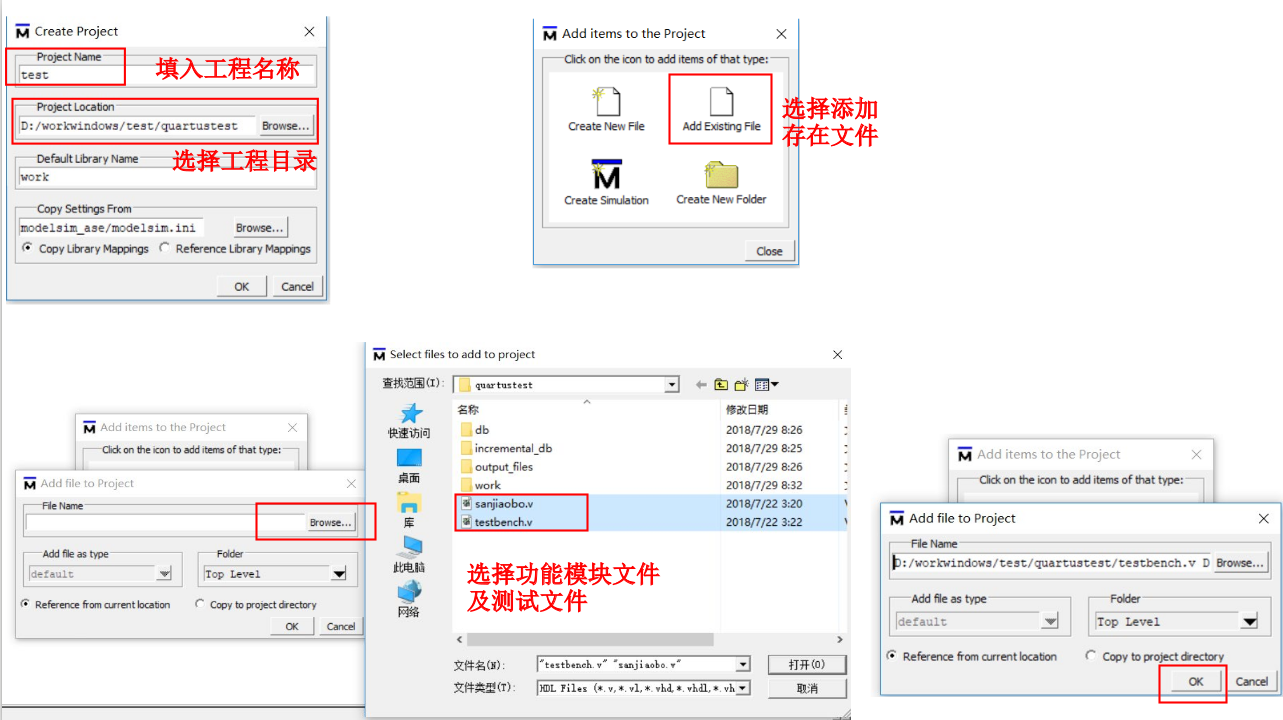

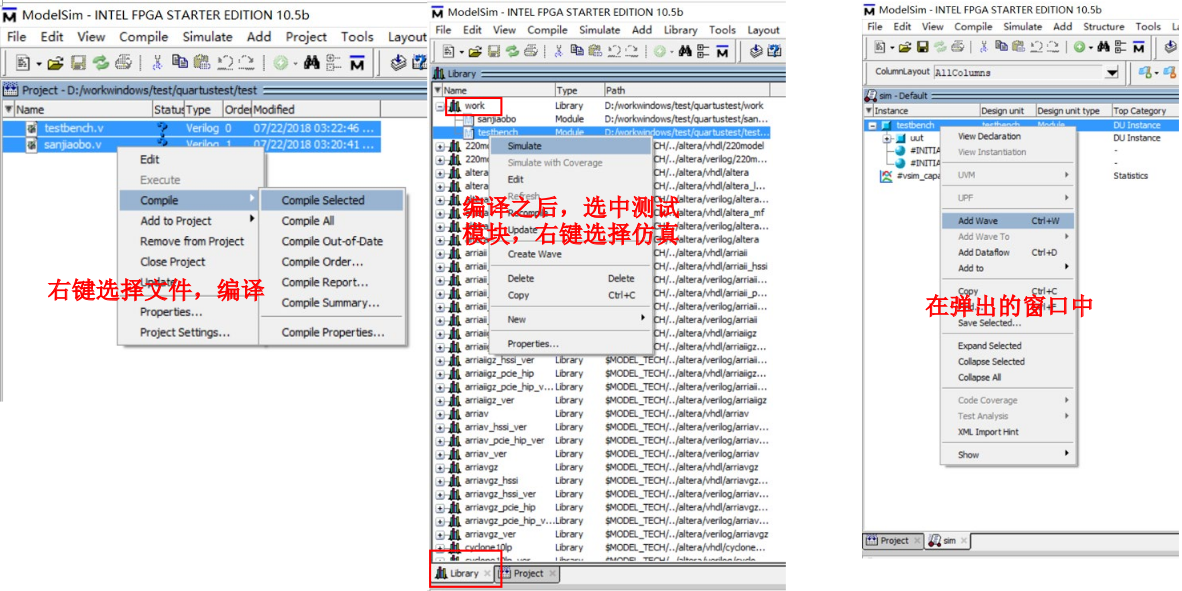

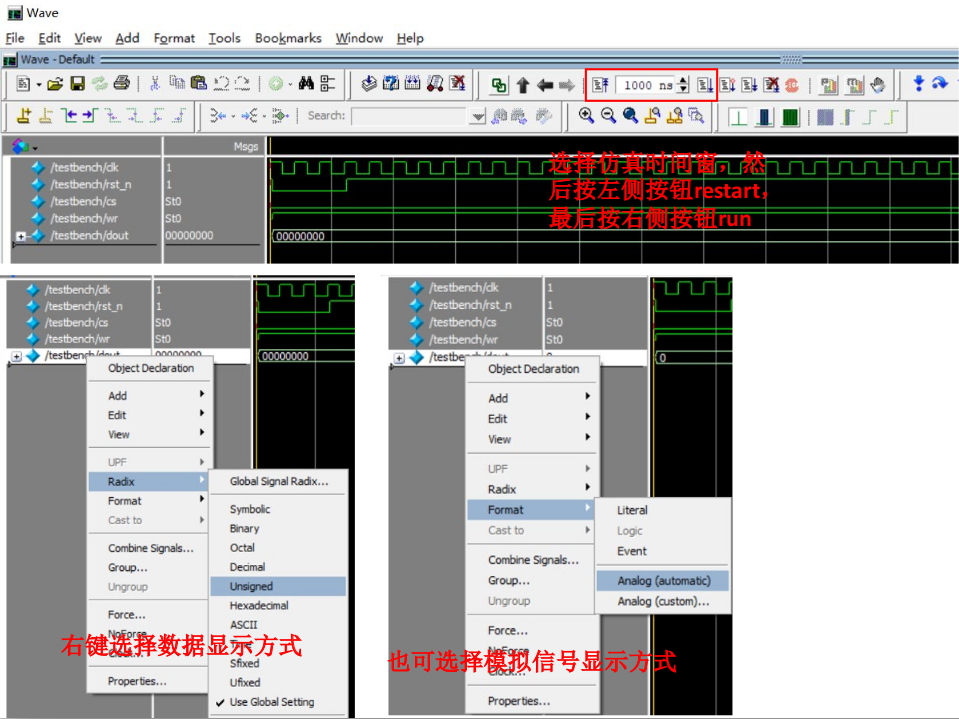

ModelSim¶

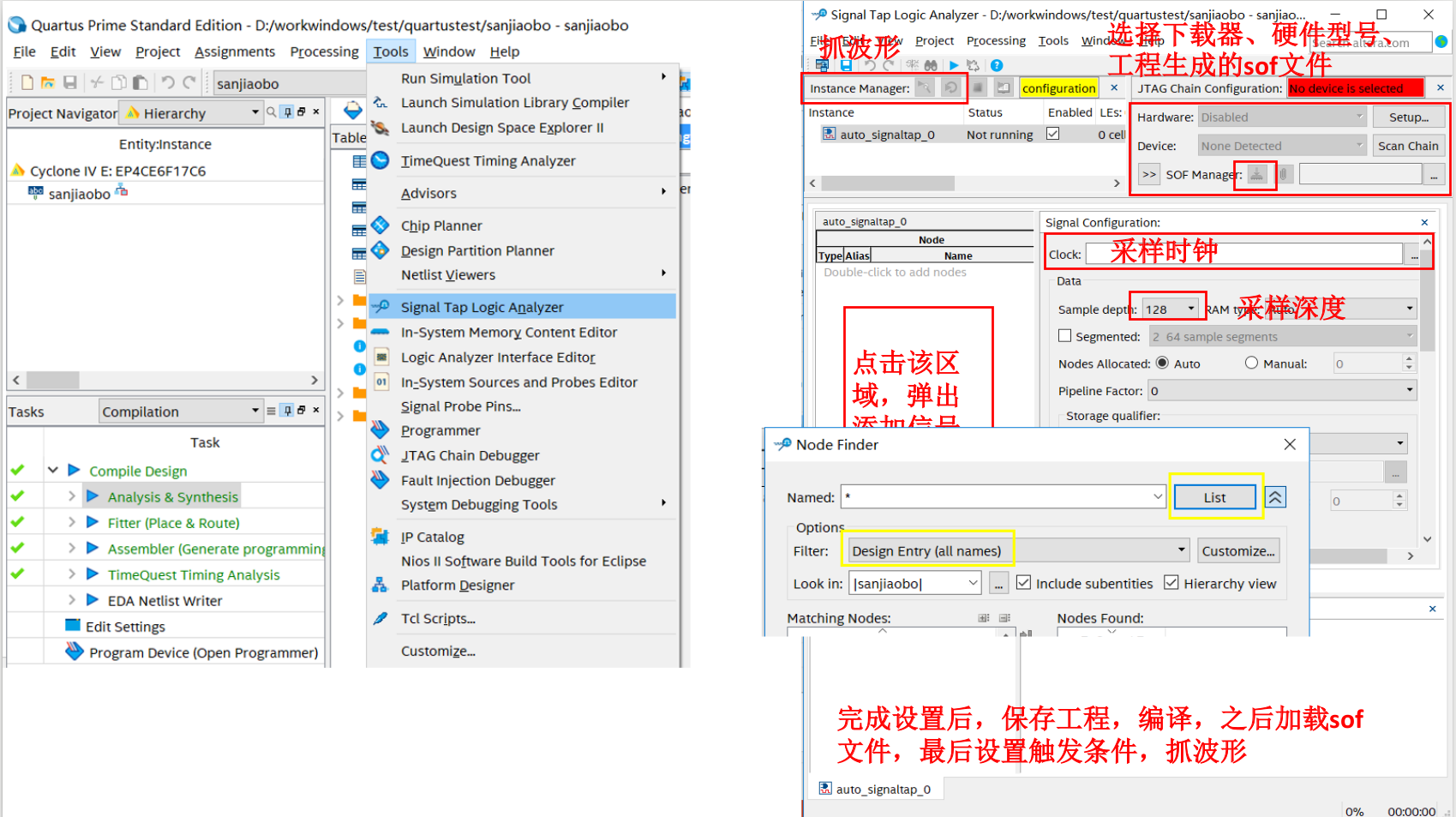

SignalTapII¶

综合属性¶

在一些应用中,有些特定的信号我们需要保留,用于进行采集检测,而综合器会自动优化把它综合掉,因此需要告诉综合器,不让它优化掉需要保留的信号。

需要保留的信号是引线

verilog HDL 定义的时候在后面增加

/* synthesis keep */

// 例如

wire keep_wire /* synthesis keep */;

VHDL 需要麻烦些,多写几行定义约束

signal keep_wire : std_logic;

attribute keep : boolean;

attribute keep of keep_wire : signal is true;

需要保留的是寄存器

verilog HDL 定义的时候在后面增加

/* synthesis noprune */ 避免优化掉没output的reg

/* synthesis preserve */ 避免將reg优化为常数,或者合并重复的reg。

// 例如

reg reg1 /* synthesis preserve */;

VHDL 同样需要麻烦些,多写几行定义约束

signal reg1 : std_logic;

attribute preserve : boolean;

attribute preserve of reg1 : signal is true;