网页控制界面¶

控制界面¶

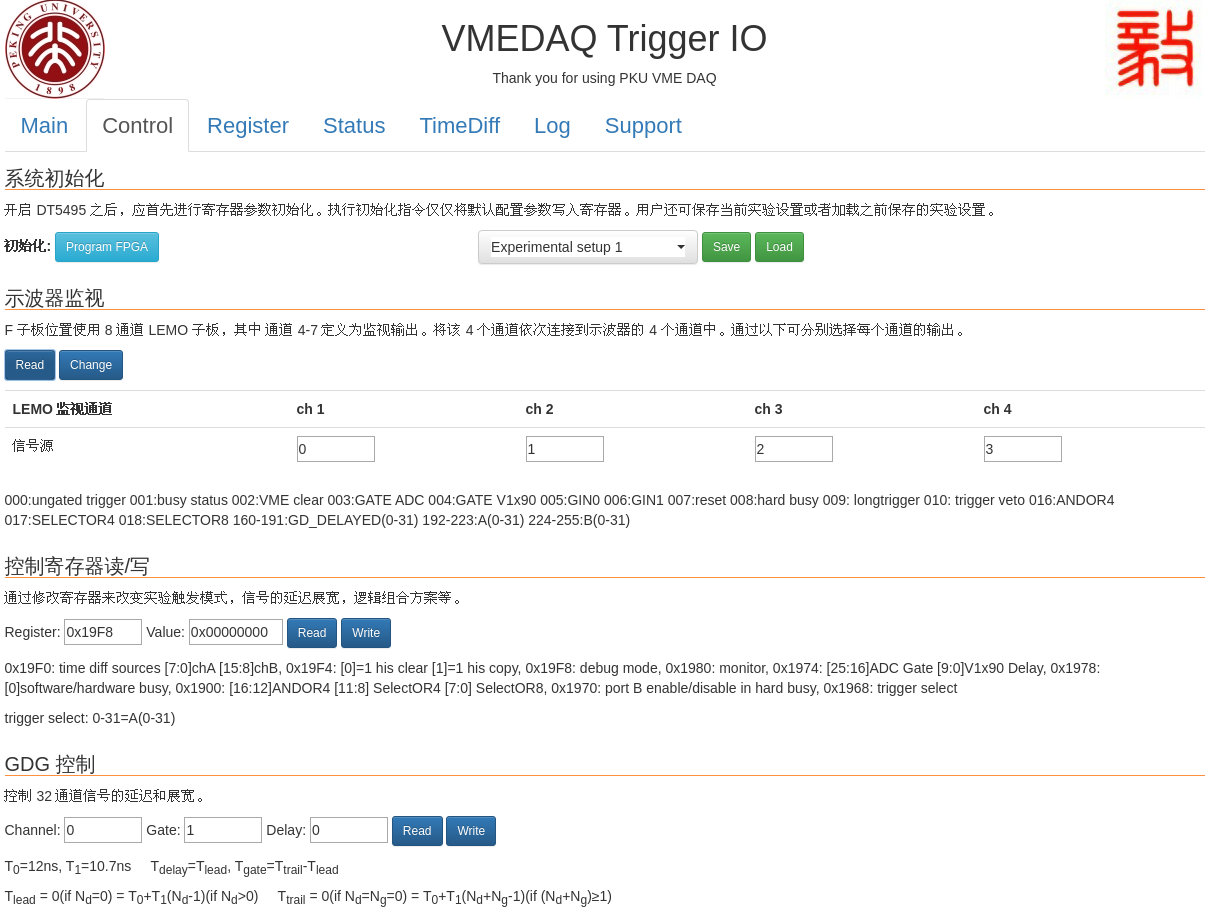

通过控制寄存器来改变实验触发模式,逻辑信号的延迟与展宽等。

按钮 “Program FPGA” 用于初始化系统配置,当可编程逻辑模块上电之后第一时间点击该按钮来完成系统的初始化。

可以保存 5 个实验设置参数,分别为 “Experimental setup 1-5”。通过修改寄存器进行实验逻辑配置之后,可以点击按钮 “Save” 保存,将会把当前 FPGA 寄存器参数保存到选定的实验配置中。按钮 “Load” 用于将选择的实验配置加载到 FPGA 中。

示波器监视部分用于选择 4 个 LEMO 输出通道的输出信号,下表中列出了当前所有可供选择的选项。点击 “Read” 按钮即可读取当前的设置参数,按钮 “Change” 用于将当前输入框的参数写入 FPGA 中。

vaule |

signal |

|---|---|

00 |

ungated trigger |

01 |

status |

02 |

clear |

03 |

gate adc |

04 |

gate 1x90 |

05 |

GIN(0) |

06 |

GIN(1) |

07 |

reset |

08 |

hardware busy |

09 |

long trigger(20 us) |

10 |

veto |

11 |

保留 |

12 |

保留 |

13 |

保留 |

14 |

保留 |

15 |

保留 |

16 |

OR32_00 |

17 |

OR32_01 |

18 |

OR32_02 |

19 |

OR32_03 |

20 |

OR32_04 |

21 |

OR32_05 |

22 |

OR32_06 |

23 |

OR32_07 |

24 |

保留 |

25 |

保留 |

26 |

保留 |

27 |

保留 |

28 |

保留 |

29 |

保留 |

30 |

保留 |

31 |

保留 |

32 |

A(0) GDG |

33 |

A(1) GDG |

34 |

A(2) GDG |

35 |

A(3) GDG |

36 |

A(4) GDG |

37 |

A(5) GDG |

38 |

A(6) GDG |

39 |

A(7) GDG |

40 |

A(8) GDG |

41 |

A(9) GDG |

42 |

A(10) GDG |

43 |

A(11) GDG |

44 |

A(12) GDG |

45 |

A(13) GDG |

46 |

A(14) GDG |

47 |

A(15) GDG |

48 |

A(16) GDG |

49 |

A(17) GDG |

50 |

A(18) GDG |

51 |

A(19) GDG |

52 |

A(20) GDG |

53 |

A(21) GDG |

54 |

A(22) GDG |

55 |

A(23) GDG |

56 |

A(24) GDG |

57 |

A(25) GDG |

58 |

A(26) GDG |

59 |

A(27) GDG |

60 |

A(28) GDG |

61 |

A(29) GDG |

62 |

A(30) GDG |

63 |

A(31) GDG |

寄存器设置部分用于读取或者修改寄存器设置参数。读取寄存器时,需要输入要读取寄存器的地址,然后点击按钮 “Read”;修改寄存器时,输入要修改寄存器的地址以及参数值,然后点击按钮“Write”。

vaule |

function |

|---|---|

0x1900 |

OR32 A[31:0] |

0x1904 |

OR32 A[31:0] |

0x1908 |

OR32 A[31:0] |

0x190C |

OR32 A[31:0] |

0x1910 |

OR32 A[31:0] |

0x1914 |

OR32 A[31:0] |

0x1918 |

OR32 A[31:0] |

0x191C |

OR32 A[31:0] |

0x1920 |

AND32 A[31:0] |

0x1924 |

AND32 A[31:0] |

0x1928 |

AND32 A[31:0] |

0x192C |

AND32 A[31:0] |

0x1930 |

AND32 A[31:0] |

0x1934 |

AND32 A[31:0] |

0x1938 |

AND32 A[31:0] |

0x193C |

AND32 A[31:0] |

0x1968 |

trigger select(见下方关于触发源的选择) |

0x1970 |

port B enable/disable in hard busy A[31:0] |

0x1974 |

[25:16]ADC Gate [9:0]V1x90 Delay |

0x0978 |

[0] software/hardware busy |

0x19F8 |

[0] debug mode(test mode pars copy when 1) |

vaule |

function |

|---|---|

00 |

A(0) |

01 |

A(1) |

02 |

A(2) |

03 |

A(3) |

04 |

A(4) |

05 |

A(5) |

06 |

A(6) |

07 |

A(7) |

08 |

A(8) |

09 |

A(9) |

10 |

A(10) |

11 |

A(11) |

12 |

A(12) |

13 |

A(13) |

14 |

A(14) |

15 |

A(15) |

16 |

A(16) |

17 |

A(17) |

18 |

A(18) |

19 |

A(19) |

20 |

A(20) |

21 |

A(21) |

22 |

A(22) |

23 |

A(23) |

24 |

A(24) |

25 |

A(25) |

26 |

A(26) |

27 |

A(27) |

28 |

A(28) |

29 |

A(29) |

30 |

A(30) |

31 |

A(31) |

32 |

OR32_00 |

33 |

OR32_01 |

34 |

OR32_02 |

35 |

OR32_03 |

36 |

OR32_04 |

37 |

OR32_05 |

38 |

OR32_06 |

39 |

OR32_07 |

40 |

AND32_00 |

41 |

AND32_01 |

42 |

AND32_02 |

43 |

AND32_03 |

44 |

AND32_04 |

45 |

AND32_05 |

46 |

AND32_06 |

47 |

AND32_07 |

GDG 控制部分用于控制 32 通道信号的延迟和展宽。

读取信号的延迟和展宽时,需要输入要读取的通道,然后点击按钮 “Read”;修改某通道的延迟和展宽时,输入要修改通道编号以及参数值,然后点击按钮“Write”。

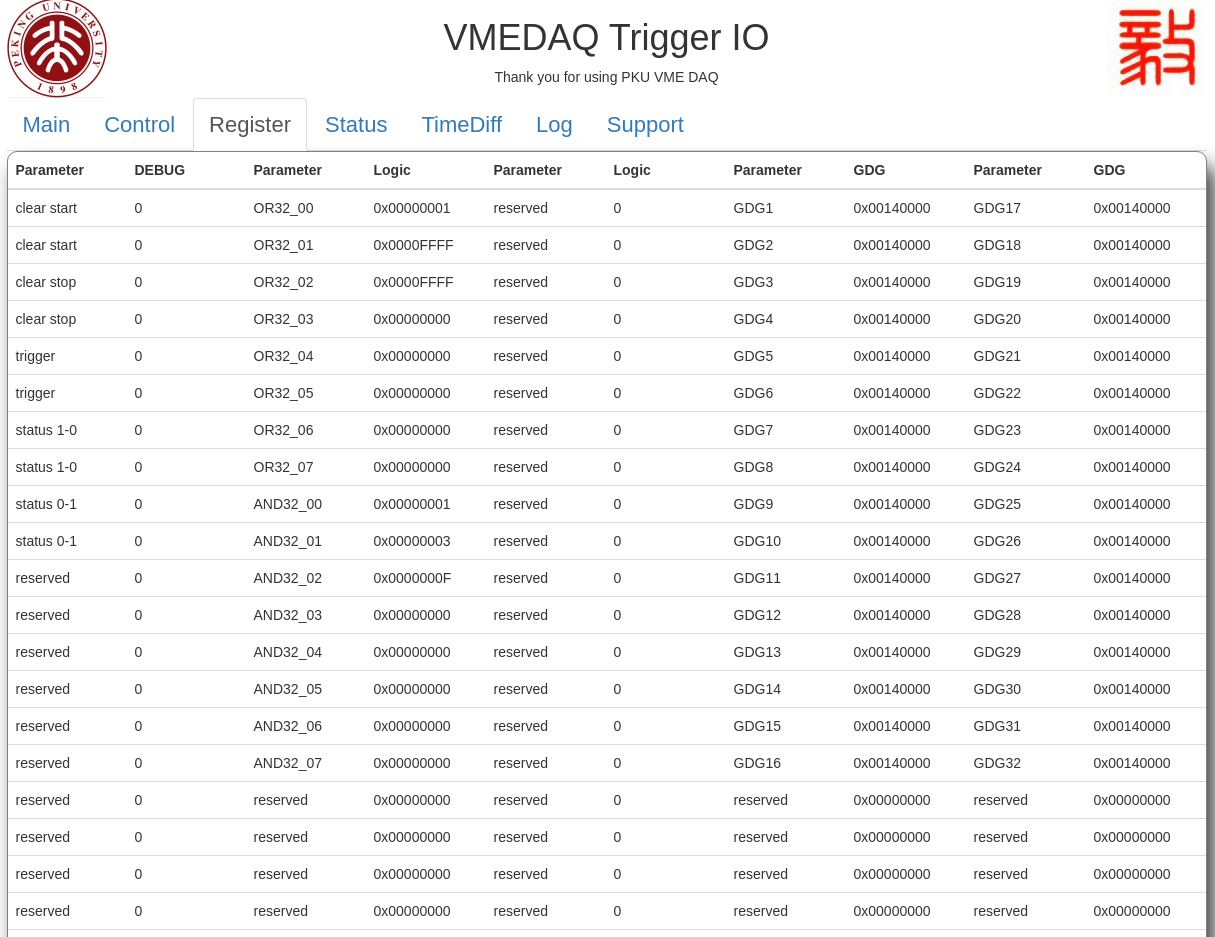

寄存器界面¶

当您访问寄存器界面时,该界面刷新一次。该界面展示了可以设置的寄存器的参数,主要用来进行参数的核查。

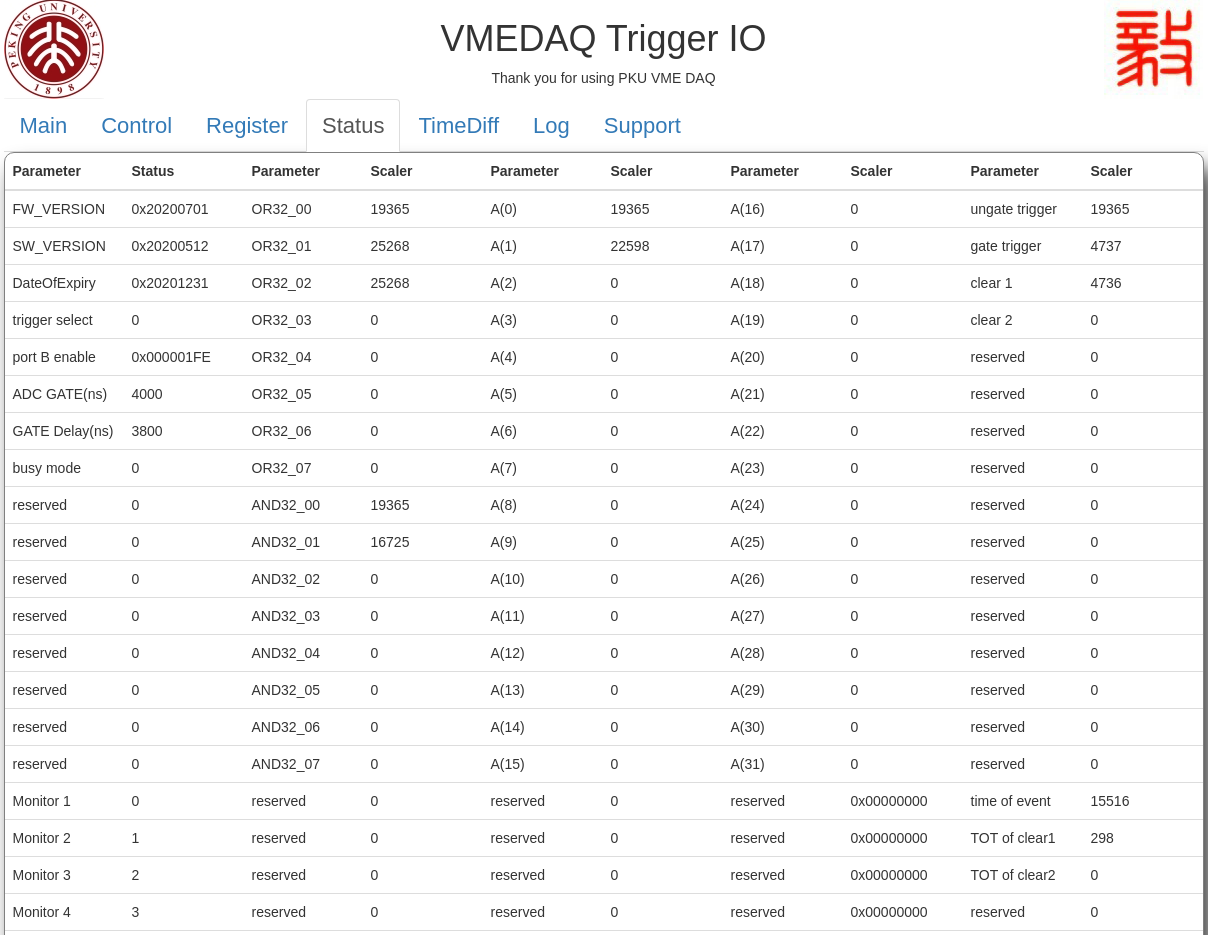

状态监视界面¶

当您访问状态页面时,该页面将每 5 秒钟自动刷新一次。

该页面主要用于实时的计数率监视。当前版本包含了 A 口 32 个输入通道的计数率,4 个 LEMO 输出通道的计数率,OR_00-07 的计数率,AND_00-07 的计数率, ungated trigger、gate trigger 等信号的计数率等。

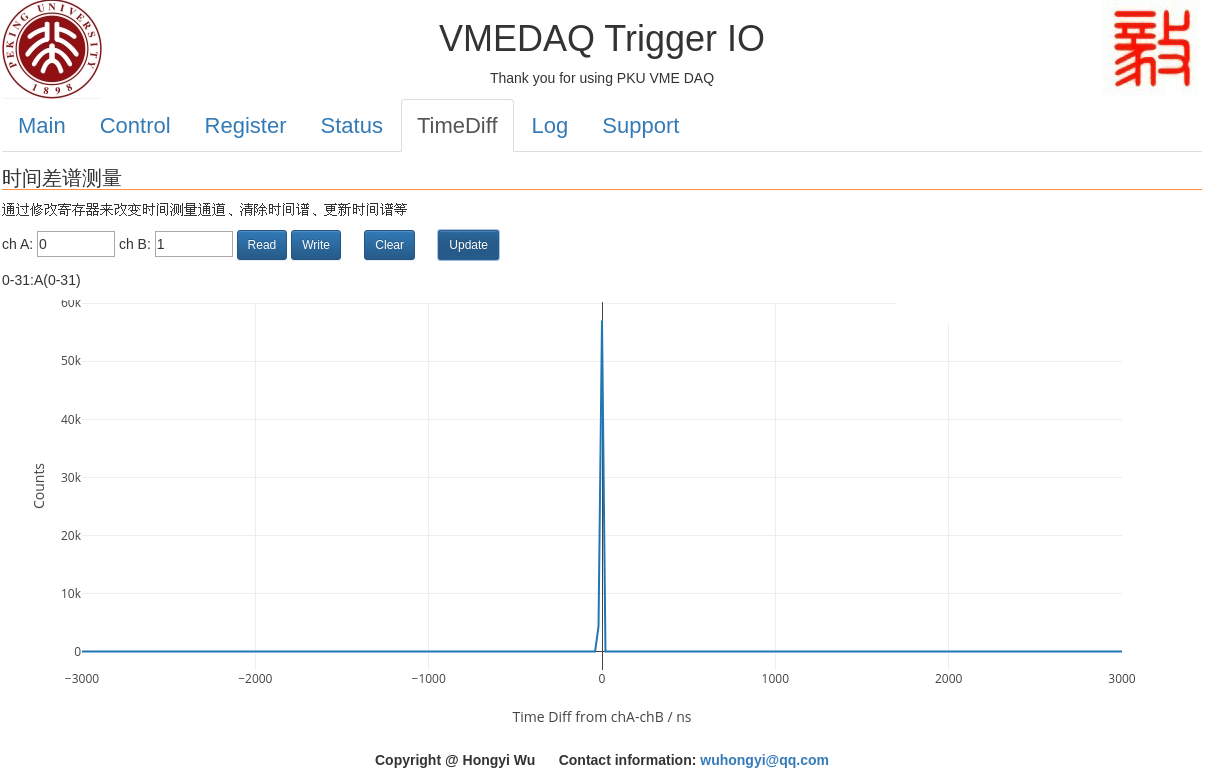

在线时间差测量¶

该页面实现了任意两个逻辑信号的时间差谱测量(chA-chB,时间差大于 0 表示 chA 信号晚于 chB 信号)。按钮 “Read” 用于读取信号源参数;按钮 “Write” 用于更改信号源;按钮 “Clear” 用于清除 FPGA 中的时间差谱,当更改信号源后必须清除 FPGA 中的时间差谱。按钮 “Update” 可用于从 FPGA 中读取当前的时间差谱并显示在网页上。

vaule |

signal |

|---|---|

00 |

A(0) GDG |

01 |

A(1) GDG |

02 |

A(2) GDG |

03 |

A(3) GDG |

04 |

A(4) GDG |

05 |

A(5) GDG |

06 |

A(6) GDG |

07 |

A(7) GDG |

08 |

A(8) GDG |

09 |

A(9) GDG |

10 |

A(10) GDG |

11 |

A(11) GDG |

12 |

A(12) GDG |

13 |

A(13) GDG |

14 |

A(14) GDG |

15 |

A(15) GDG |

16 |

A(16) GDG |

17 |

A(17) GDG |

18 |

A(18) GDG |

19 |

A(19) GDG |

20 |

A(20) GDG |

21 |

A(21) GDG |

22 |

A(22) GDG |

23 |

A(23) GDG |

24 |

A(24) GDG |

25 |

A(25) GDG |

26 |

A(26) GDG |

27 |

A(27) GDG |

28 |

A(28) GDG |

29 |

A(29) GDG |

30 |

A(30) GDG |

31 |

A(31) GDG |

32 |

OR32_00 |

33 |

OR32_01 |

34 |

OR32_02 |

35 |

OR32_03 |

36 |

OR32_04 |

37 |

OR32_05 |

38 |

OR32_06 |

39 |

OR32_07 |

40 |

AND32_00 |

41 |

AND32_01 |

42 |

AND32_02 |

43 |

AND32_03 |

44 |

AND32_04 |

45 |

AND32_05 |

46 |

AND32_06 |

47 |

AND32_07 |

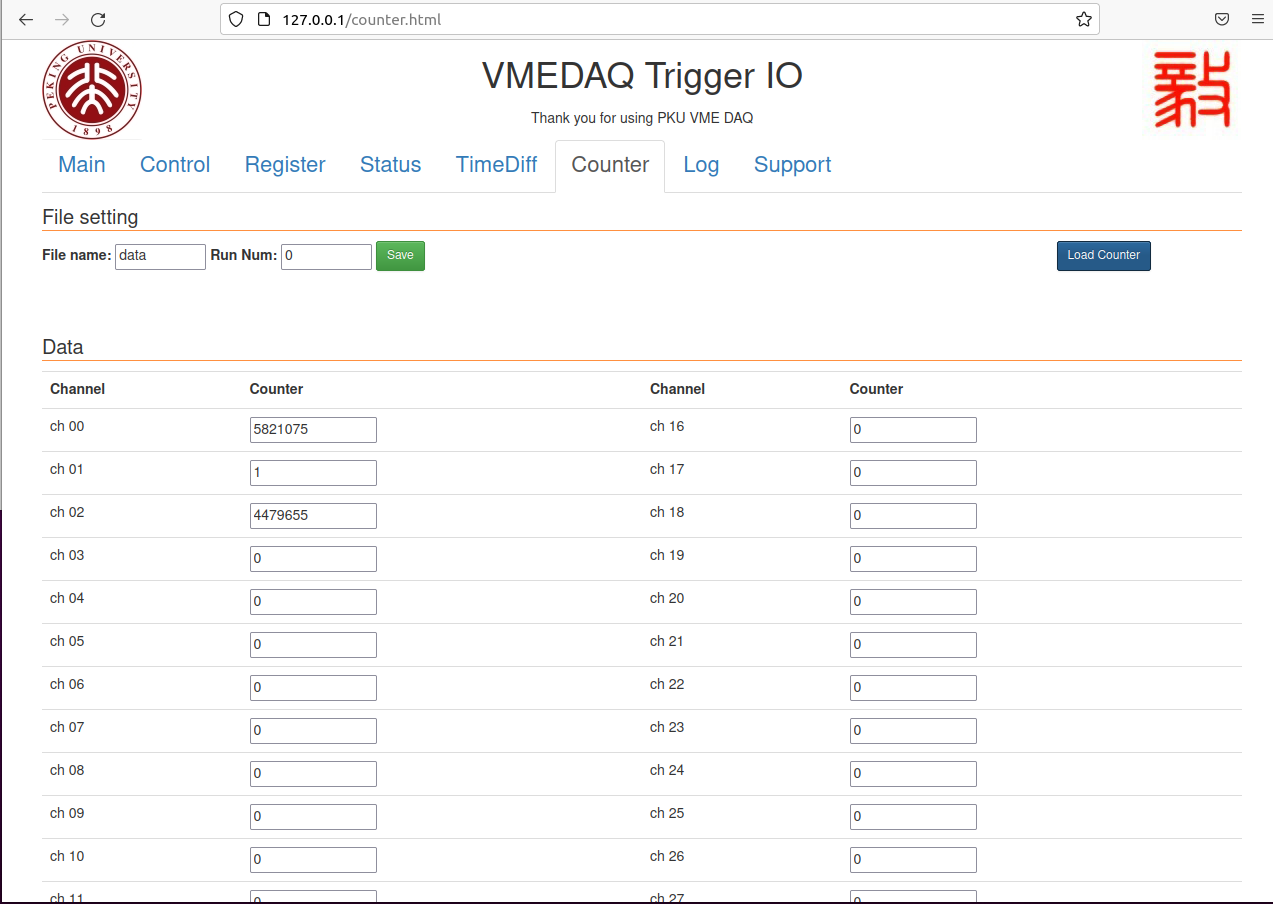

计数器¶

该页面实现了 x495 A 输入口 32 通道的计数器功能。使用该功能需要将 V1718/V2718 port 3 连接到 G1 口。当检测到 port 3 口脉冲下降沿时,计数开始,当 port 3 信号为低电平时进行计数。可随时读取计数状态,也可将计数结果保存在文件中。