## VHDL入门·解惑·经典实例·经验总结

责任编辑:王 鸿

封面设计: runsigness

ISBN 7-81077-589-8 定价: 22.00元

电子设计竞赛・课程设计・毕业设计 オチムギ

## VHDL入门・解惑・经典实例 ・经验总结

黄 任 编著

北京航空航天大管出版社

#### 内容简介

本书分 4 部分对 VHDL 进行了系统的介绍。第 1 部分为人门篇,介绍了 VHDL 的常用语法及利用 VHDL 实现系统层次化设计的方法;第 2 部分为解惑篇,详细解答了 VHDL 初学者常见的一些问题;第 3 部分为实例篇,包括多个常用单元电路的 VHDL 程序和包括数字频率计在内的多个经典人门题目的参考程序,并给出了 2002 年北京市大学生电子设计竞赛(EDA 专项)的参考设计;第 4 部分为经验篇,对一些 VHDL 语句的可综合性进行探讨,并给出了 6 种可综合的进程语句的模板。

本书内容详实,语言通俗、易懂,附带大量经典人门练习题及其参考设计,可以帮助初学者在短时间内人门,可作为全国大学生电子设计竞赛的培训材料、电子科技活动的参考资料,也可供电子爱好者及高等院校的师生在进行数字电路设计实验时参考。

#### 图书在版编目(CIP)数据

VHDL 人门·解惑·经典实例·经验总结/黄任编著. 北京:北京航空航天大学出版社,2005.1 ISBN 7-81077-589-8

I. V··· Ⅱ. 黄··· Ⅲ. 硬件描述语言,VHDL IV. TP312

中国版本图书馆 CIP 数据核字(2004)第 132708 号

VHDL 入门・解惑・经典实例・经验总结 黄 任 编著 责任编辑 王 鴻

北京航空航天大学出版社出版发行 北京市海淀区学院路 37 号(100083) 发行部电话:010-82317024 传真:010-82328026 http://www.buaapress.com.cn E-mail:bhpress@263.net 涿州市新华印刷有限公司印装 各地书店经销

> 开本:787×960 1/16.印张:16.75 字数:375千字 2005年1月第1版 2005年1月第1次印刷 印数:5000册 ISBN 7-81077-589-8 定价:22.00元

献给散爱的郭莉老师,我的父亲黄禄河、母亲周欣和林林黄正及所有曾经教过我的老师,感谢他(牠)们一直以来给予我的支持和无限吴怀。

## 本书的特点

市面上关于 VHDL 的书汗牛充栋,为什么作者还要不辞辛苦地添砖加瓦呢?如果你抱有这种怀疑态度,不妨将本书与其他的 VHDL 教材比较一下,会发现本书有以下特点:

#### (1) 真正面向初学者

与其他入门的书不同,本书不求博大精深,只求深入浅出。本书并未覆盖VHDL的所用语法,因为有些语法不但艰深,而且一般的设计根本不会用到。学习这些语法不但无助于初学者设计水平的提高,反而容易挫伤初学者学习VHDL的积极性。很多VHDL门外汉都渴望有一本能把他们带入VHDL设计大门的真正的入门教程。为了保证初学者能看懂本书,作者每写完一章就请没有学过VHDL语言的学生试读,并根据他们的意见对书稿进行修改,因此本书虽然无法做到老妪能懂,但对有一定数字设计基础的读者来说是浅显易懂的。

#### (2) 可综合的 VHDL 语言

VHDL语句大体上可以分为两种:一种是只可仿真,不可综合(即不能用硬件实现)的语句;另一种则是可综合的语句。对初学者来说,学习 VHDL语言大都是为了在 CPLD/FPGA 上实现数字电路设计,因此语句的可综合性就十分重要。本书是一本面向实际应用的入门教程,书中所用语句均为可综合的 VHDL语句,所有程序均在实验仪上调试通过。

## (3) 内容全面,学、练结合

本书分为入门篇、解惑篇、实例篇和经验篇 4 部分,这几部分相辅相成,可以帮助读者在最短的时间内掌握 VHDL 语言。值得一提的是,实例篇中所用的题

目均是北京邮电大学信息工程学院的学生在准备 2002 年北京市大学生电子设计竞赛所做的练习。实践证明,这些题目对提高初学者的 CPLD/FPGA 开发水平是很有帮助的(经过两个月的训练,参赛学生有一半获得一等奖,而且成绩在获一等奖的学生中名列前茅)。本书给出的例程均为获一等奖学生的作品,具有参考价值。

#### 本书的结构

本书分为4部分,各部分的内容简介如下:

#### (1) 入门篇

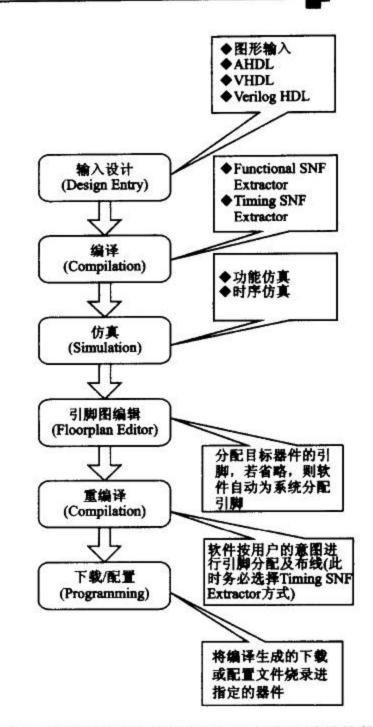

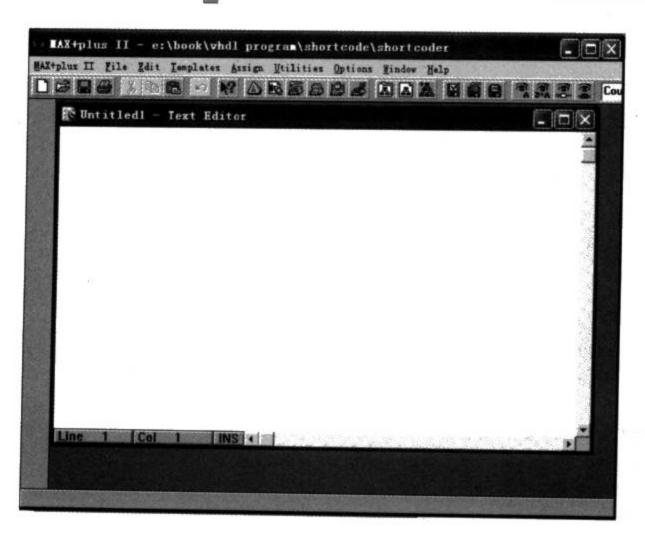

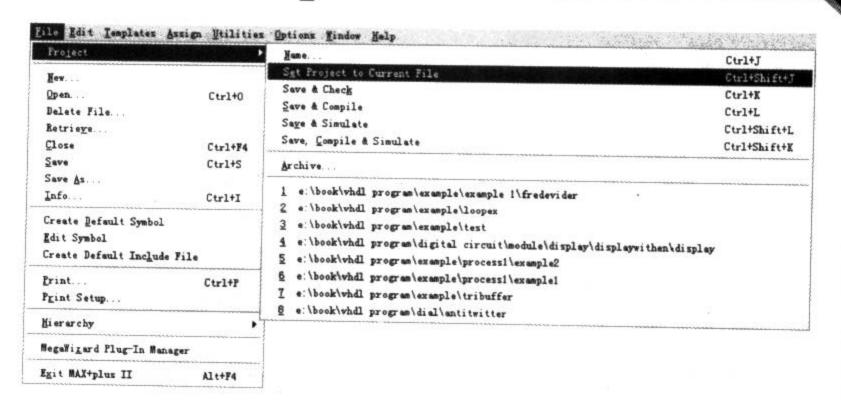

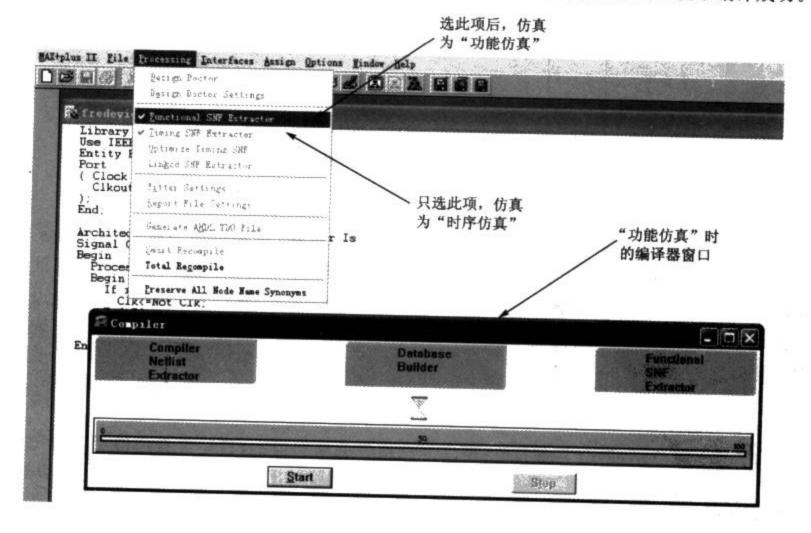

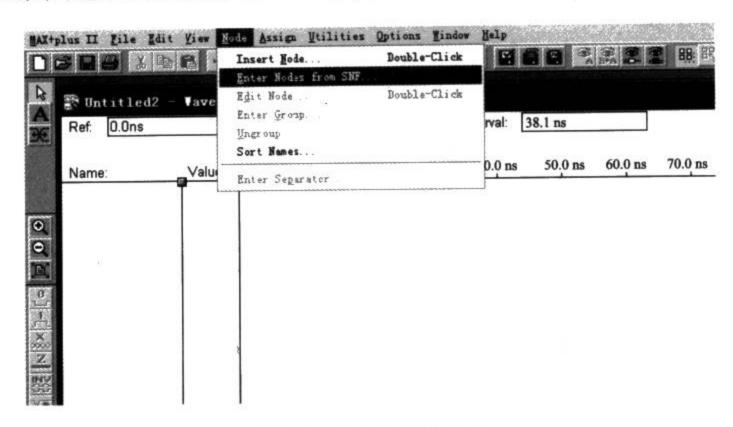

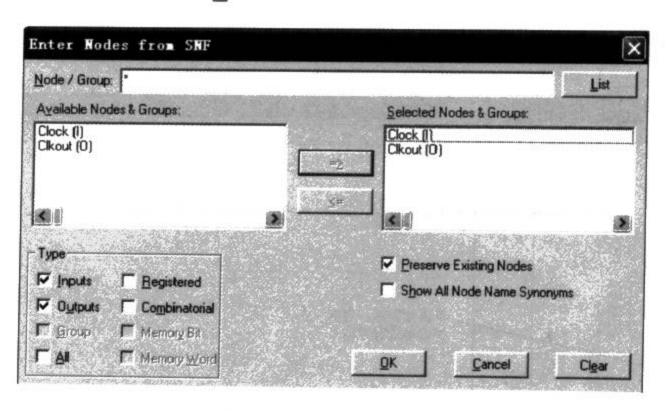

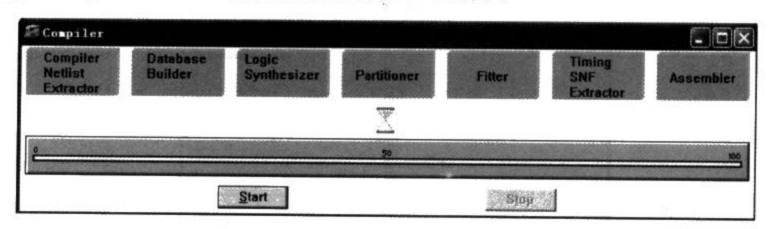

简要介绍 VHDL 语言的特点和设计流程;通过大量的简单实例深入浅出地讲解了 VHDL 的基本结构、数据类型和语法;介绍了 Moore 状态机和 Mealy 状态机在 VHDL 中的实现方法;介绍如何在 MAX+plus II 中采用图形法与文本法结合的混合输入方法实现元件重用与系统的层次化设计;最后,介绍了元件例化、程序包及类属映射等 VHDL 进阶语句,以及利用这些语句实现系统层次化设计的方法。

#### (2) 解惑篇

对初学者常见的一些问题(包括设计方法、仿真与综合以及 MAX+plus II 的使用等方面)进行详细的解答。

#### (3) 实例篇

给出了分频电路、七段数码管驱动电路、SRAM读/写电路等常用单元电路的VHDL程序;详细讲解了交通灯控制器、乒乓球游戏机、数字频率计、WCDMA短码生成器、Franaszek码编解码器等系统的设计方法,并给出了源程序,同时给出了2002年北京市大学生电子设计竞赛题——自动打铃系统的系统框图和参考程序;此外,在每章后附加了练习题,读者可以通过这些题目的训练,迅速提高VHDL设计水平。

#### (4) 经验篇

对 LOOP 语句和进程语句的可综合性进行了探讨,并给出了 6 种可综合的进程语句的模板,最后介绍了 VHDL 可综合编程的一般规则。

## 配套书籍

如果读者学完本书后想进一步了解 CPLD/FPGA 与单片机的综合应用,那么请参考北京航空航天大学出版社出版的本丛书中的《AVR 单片机与 CPLD/

FPGA综合应用入门》。该书系统论述了单片机与 CPLD/FPGA 之间的通信和合作方法,并全面阐述了高精度频率计、数控波形发生器、简易逻辑分析仪等单片机与 CPLD/FPGA 综合应用系统的设计思想和具体实现方法。《VHDL入门·解惑·经典实例·经验总结》既是该书第3章的扩展,又可作为该书的基础教程,二者相辅相成,可帮助读者在最短时间内掌握单片机和 CPLD/FPGA 的应用。

## 致 谢

本书在编写过程中,得到了北京邮电大学信息工程学院创新实验室主任郭莉副教授的大力帮助与支持。郭莉老师带领创新实验室的学生参加了多次电子设计竞赛,取得令人瞩目的成绩,参赛学生获奖率为100%,其中一半的学生获得了一等奖。郭莉老师在百忙之中仍仔细审阅了全书,并提出了许多宝贵的意见,在此向她表示衷心的感谢。

本书在正式出版前,曾作为北京邮电大学信息工程学院创新实验室的内部教材,用以指导学生参加各种电子设计竞赛。本书得到了学生的肯定,也从参赛学生那里得到了很多反馈意见。在此要特别感谢杨芳芳、张万能、赵荣华、于光炜、刘阳、赵莹、王志勇、胡子明等同学,他们的意见对本书的改进起到了十分关键的作用。

特别值得一提的是,掌字公司(http://www.kandh.com.cn)为作者提供了实验仪。本书中所有程序均在该实验仪上调试通过,在此对于掌字公司的大力支持表示感谢。

此外,本书的练习题部分选自北京邮电大学信息工程学院田宝玉副院长的《VHDL》课程练习和电路中心的《数字逻辑电路实验》课程讲义,在此一并致谢。

## 本书的相关网站

本书的相关网站地址为 http://www.ele-contests.com。本网站提供本书中部分源程序以及一些 VHDL 相关资料的下载。

如果在阅读本书的过程中发现任何错误,或是有任何改进本书的建议,请通过 huangren@ieee.org与作者联系,最新的勘误表将会在本书的相关网站上登出。

> 作 者 于韩国国立汉城大学 SOC Center 2004 年 12 月

## 入门篇

| 44 1 |   | VIII to | 177 |

|------|---|---------|-----|

| 第 1  | - | VHDL 初挂 | ж   |

|   | 1. |                                             |            |                              |                                              |                          |          |           |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | ••••                                    |             |                                        |

|---|----|---------------------------------------------|------------|------------------------------|----------------------------------------------|--------------------------|----------|-----------|----------|-----------------------|-----------|-------|-----------------|-------------------------------|------|------|------------------|------|-------|------|------|------|------|---------------------------------------|------|-------|-----------|-------|-------|-------|------|-----------------------------------------|-------------|----------------------------------------|

|   |    | 1                                           | . 1        | l. :                         |                                              |                          |          |           |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | ••••                                    |             |                                        |

|   |    |                                             |            | ١. :                         |                                              |                          | 17.00    |           | 3.55     |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | ••••                                    |             |                                        |

|   |    |                                             |            |                              |                                              |                          |          |           |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | ••••                                    |             |                                        |

|   | 1. | 2                                           |            | V                            |                                              |                          |          |           |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | ••••                                    |             |                                        |

|   |    | 1                                           | . 2        | 2. :                         | 1                                            | 设                        | it       | 输         | X        |                       | •••       | •••   | •••             | ••••                          | •••• | •••  | •••              | •••• | •••   | •••• | •••• | •••  | •••  | ••••                                  | •••• | ••••  |           | ••••  | ••••• | ••••  | •••• | ••••                                    | ••••        | 7                                      |

|   |    |                                             | Š          | 20                           |                                              |                          |          | •         |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | •••••                                   |             |                                        |

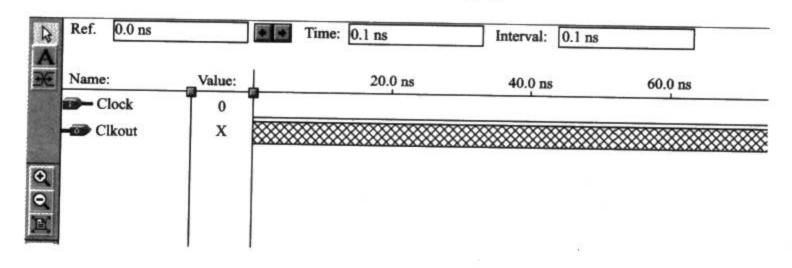

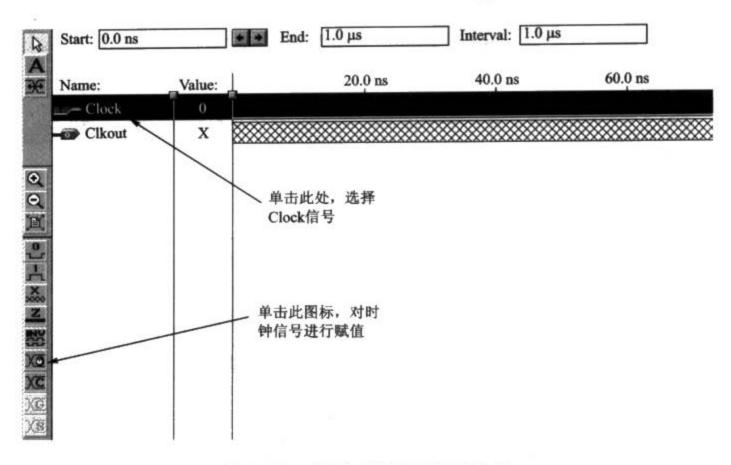

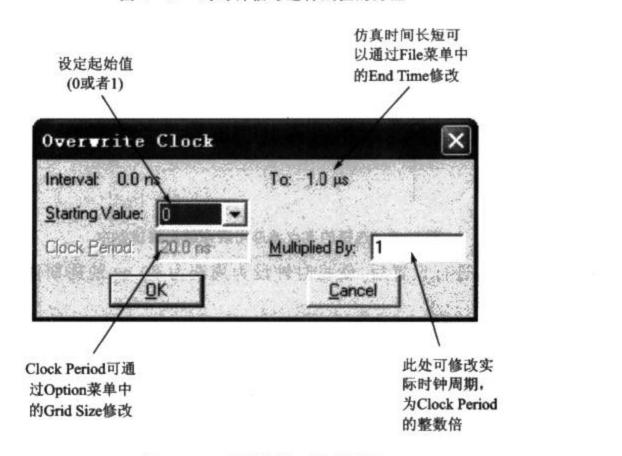

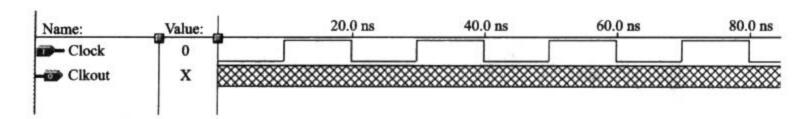

|   |    | 1                                           | . 2        | 2. 3                         | 3                                            | 仿                        |          | 真         | ••       | •••                   | •••       | ••••  | •••             | •••                           | •••• | •••  | •••              | •••• | •••   | •••  | •••• | •••  |      | • • • •                               | •••  | ••••  | ••••      | ••••  | ••••  | ••••• | •••• | •••••                                   | ••          | 12                                     |

|   |    |                                             |            | 2.                           |                                              |                          | •        |           |          | -                     |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | • • • • •                               |             |                                        |

|   |    | 1                                           | . 2        | 2. 5                         |                                              |                          |          |           |          |                       |           |       | 3777500         |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | •••••                                   |             |                                        |

|   |    | 1.                                          | . 2        | 2. 6                         |                                              | 7.77                     |          | 1000      |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | •••••                                   |             |                                        |

|   |    | 1.                                          | . 2        | 2. 7                         | 7                                            | 实                        | 示        | 验         | ù        | E••                   | •••       | •••   | •••             | • • • •                       | •••• | •••  | •••              | •••• | •••   | •••• | •••• | •••• | •••• | • • • •                               | •••  | ••••  | •••••     |       | ••••  | ••••• | •••• | •••••                                   | ••          | 19                                     |

|   |    |                                             |            |                              |                                              |                          |          |           |          |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      |                                         |             |                                        |

| 第 | 2  | 1                                           | Ė          |                              | VH                                           | DL                       | )        | ď         | 7        |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      |                                         |             |                                        |

| • |    |                                             |            |                              |                                              |                          |          |           |          | 吉村                    | 构         | ••    | •••             |                               |      | •••  | •••              | •••• | •••   |      | •••• |      |      |                                       | •••  |       |           | ••••  | ••••  | ····  |      | ••••                                    | ;           | 20                                     |

| • | 2. | 1                                           |            | V                            | HI                                           | DL                       | 程        | 序         | 4        |                       |           |       |                 |                               |      |      |                  |      |       |      |      |      |      |                                       |      |       |           |       |       |       |      | ••••                                    |             |                                        |

| • | 2. | 1<br>2.<br>2.                               | . 1        | V<br>. 1                     | 'HI<br>1<br>2                                | DL<br>实<br>结             | 程构       | 序体体       | <b>4</b> | • • •                 | •••       | •••   |                 | • • • •                       | •••  | •••  | •••              | •••• | •••   |      | •••• |      | •••  | · · · ·                               | •••• | ••••• |           | ••••  | ••••  |       |      | • • • • • • • • • • • • • • • • • • • • | ;           | 22<br>24                               |

| • | 2. | 1<br>2.<br>2.                               | . 1        | V<br>. 1                     | 'HI<br>1<br>2                                | DL<br>实<br>结             | 程构       | 序体体       | <b>4</b> | • • •                 | •••       | •••   |                 | • • • •                       | •••  | •••  | •••              | •••• | •••   |      | •••• |      | •••  | · · · ·                               | •••• | ••••• |           | ••••  | ••••  |       |      | ••••                                    | ;           | 22<br>24                               |

| į | 2. | 1<br>2.<br>2.                               | . 1<br>. 1 | V<br>. 1                     | HI<br>1<br>2                                 | DL<br>实<br>结<br>库        | 程构与      | 序体体包      | 4 的      | ····<br>)诉            |           | ···   | <br>            | <br>                          | •••• |      |                  | •••• |       |      |      |      |      | <br><br>                              | •••• | ••••• | · · · · · | ••••• | ••••• |       |      | • • • • • • • • • • • • • • • • • • • • | <br>;       | 22<br>24<br>26                         |

| į | 2. | 1<br>2.<br>2.<br>2.<br>2.                   | . 1        | V<br>. 1                     | HI<br>1<br>2<br>3<br>HI                      | DL<br>实结库<br>DL          | 程构与基     | 序体体包本     | 4        | <br>) 调<br>女 <b>.</b> | 明月 居主     | 月…    | <br>            | · · · ·<br>· · · ·<br>· · · · |      | <br> |                  |      | ••••  |      | •••• |      |      | · · · · · · · · · · · · · · · · · · · | •••• |       |           |       |       |       |      | •••••                                   | ;<br>;      | 22<br>24<br>26<br>27                   |

| į | 2. | 1<br>2.<br>2.<br>2.<br>2.                   | . 1        | V<br>                        | HI<br>1<br>2<br>3<br>HI                      | DL<br>实结库DL<br>VF        | 程构与基订    | 序体体包本儿    | 4 的 要 五  |                       |           | 大型 类型 | ····<br>过<br>女技 | ····<br>····<br>居类            |      | •••  |                  |      | ••••  |      |      |      |      |                                       | •••• |       |           |       |       |       |      | •••••                                   | ;<br>;<br>; | 22<br>24<br>26<br>27<br>27             |

| į | 2. | 1<br>2.<br>2.<br>2.<br>2.<br>2.             | . 1        | V<br>. 1<br>. 3<br>V<br>2, 1 | HI<br>1<br>2<br>3<br>HI<br>1<br>1            | DL<br>实结库DL<br>VF<br>IEI | 程构与基础证   | 序体体包本儿子   | 当的要更     | … 游女质定                |           | 1     | 过 女排:           |                               | 型量位  | ···· | …<br>…<br>…<br>与 | 天量   | <br>t |      |      |      |      |                                       |      |       |           |       |       |       |      |                                         | ·· ;        | 22<br>24<br>26<br>27<br>27             |

|   | 2. | 1<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2. | . 1        | V                            | HI<br>1<br>2<br>3<br>HI<br>1<br>2            | DL 实结库 DL VI IEI 用       | 程构与基础正立  | 序体体包本儿子自  | 当·· 的    |                       | 明 居 之 义 的 |       |                 |                               | 型型型  | ···· | 与                | 天量   |       |      |      |      |      |                                       |      |       |           |       |       |       |      |                                         |             | 22<br>24<br>26<br>27<br>27<br>31       |

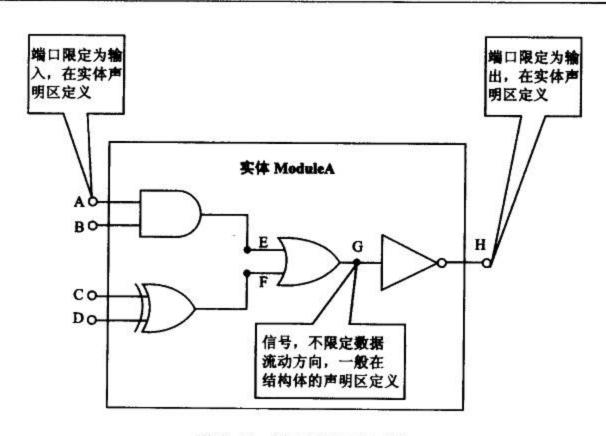

|   | 2. | 1<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>3  | . 1        | V                            | H1<br>1<br>2<br>3<br>H1<br>1<br>2<br>3<br>H1 | DL 实结库 DL VI IEI 用 DL    | 程构与基础区立数 | 序体体包本儿子自据 | 当的要更页定文  |                       |           |       | 2 女性症           |                               | 型量位型 | ···· |                  | 天量   | t ·   |      |      |      | •••• |                                       |      |       |           |       |       |       |      |                                         | ;           | 22<br>24<br>26<br>27<br>27<br>31<br>32 |

|          |      | 2     | 2. 3   | 3. 2       | 变                                            | 量            | ţ     | •••• | • • • • • • • • • • • • • • • • • • • • | • • • • • • •                           | • • • • | • • • • • • |           | ••••• | ••••      | • • • • • |         | ••••      | •••••     | ••••  | ••••      | ••••      | • • • • •   | •••••       | ••••  | 36  |

|----------|------|-------|--------|------------|----------------------------------------------|--------------|-------|------|-----------------------------------------|-----------------------------------------|---------|-------------|-----------|-------|-----------|-----------|---------|-----------|-----------|-------|-----------|-----------|-------------|-------------|-------|-----|

|          |      | 2     | 2. 3   | . 3        | 常                                            | 数            | (•••• |      | • • • • • • • • • • • • • • • • • • • • | • • • • • •                             | • • • • | • • • • • • | •••••     | ••••  | •••••     | • • • • • | ••••    | • • • • • | •••••     | ••••  | • • • •   | ••••      | • • • • •   | •••••       | ••••  | 37  |

|          | 2    | . 4   | ļ      | VH         | DL                                           | 运算           | ¥符    | ••   | • • • • • •                             | • • • • • • •                           | • • • • | • • • • • • | ••••      | ••••  | •••••     | ••••      | ••••    | • • • • • | •••••     | ••••  | • • • •   | ••••      | • • • • •   | •••••       | ••••• | 38  |

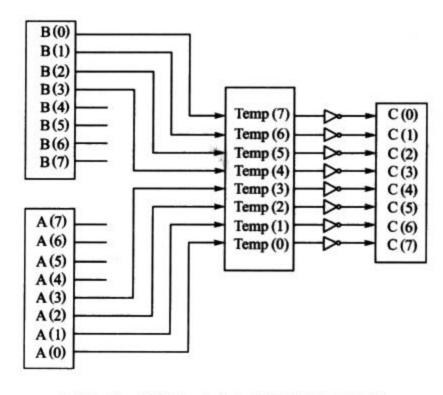

|          |      | 2     | 2. 4   | . 1        | 算                                            | 术运           | 算名    | Ŧ    | • • • • • •                             | • • • • • • •                           | • • • • |             |           | ••••  | •••••     | ••••      |         |           | •••••     | ••••  | • • • •   | ••••      |             | •••••       |       | 39  |

|          |      | 2     | . 4    | . 2        | 并                                            | 置运           | 算名    | Ŧ    | • • • • • •                             |                                         | • • • • | •••••       |           | ••••  |           |           |         |           |           | ••••  | • • • •   | ••••      |             | •••••       | ••••• | 39  |

|          |      | 2     | . 4    | . 3        | 关                                            | 系运           | 算?    | Ŧ    | • • • • • •                             |                                         | • • • • | •••••       | • • • •   | ••••  | • • • • • |           |         |           | •••••     | ••••  | • • • •   | ••••      | · •         | •••••       |       | 40  |

|          |      | 2     | . 4    | . 4        | 逻                                            | 揖运           | 算名    | Ŧ    | • • • • • •                             | • • • • • • • • • • • • • • • • • • • • | • • • • | ••••        | ••••      | ••••  | ••••      | ••••      | ••••    | • • • • • | ••••      | ••••  | • • • • • | ••••      | • • • • •   | •••••       | ••••• | 40  |

|          | 2    | . 5   |        | VH         |                                              |              |       | 3.00 |                                         | • • • • • • • •                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       | 2.3 |

|          |      |       | 00.000 | . 1        |                                              |              |       |      |                                         | J                                       |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          |      |       |        |            | C. S. C. | 2010/03/2010 |       |      |                                         | • • • • • • •                           |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       | _   |

|          | 2    | . 6   | (c)    | VH         |                                              |              |       |      |                                         | • • • • • • • • • • • • • • • • • • • • |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          |      |       |        | . 1        |                                              |              |       |      |                                         | • • • • • • • • • • • • • • • • • • • • |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          |      | 2     | . 6    | . 2        | 流                                            | 星控           | 制语    | 句    | ••••                                    | • • • • • • • • • • • • • • • • • • • • | •••     | ••••        | ••••      | ••••  | ••••      | ••••      | •••••   | • • • • • | •••••     | ••••  | • • • • • | •••••     | ••••        |             | ••••• | 56  |

| 第        | 3    | 1     | t      | 状          | 态机                                           | 在            | VHD   | )L   | 中的                                      | 实现                                      |         |             |           |       |           |           |         |           | 25        |       |           |           |             |             |       |     |

| 8000     |      | - 636 | 6.000  | 45000      |                                              | 300 E-1136   |       |      | tuditi.                                 | 507)(7 <del>7</del> 7)                  |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

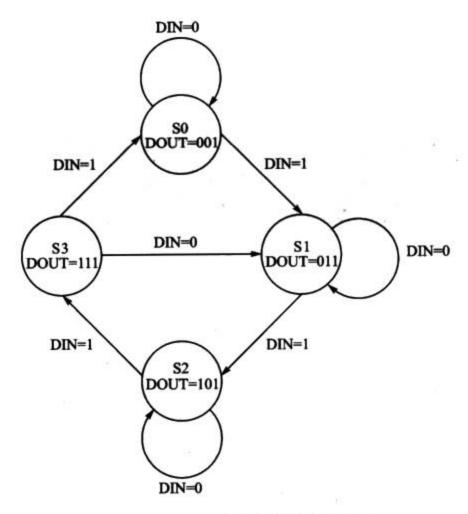

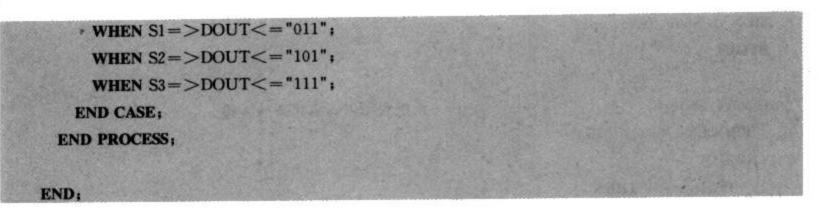

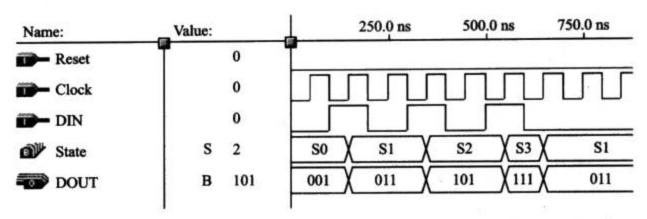

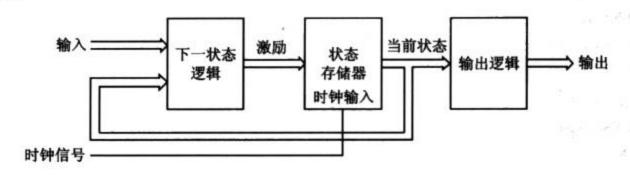

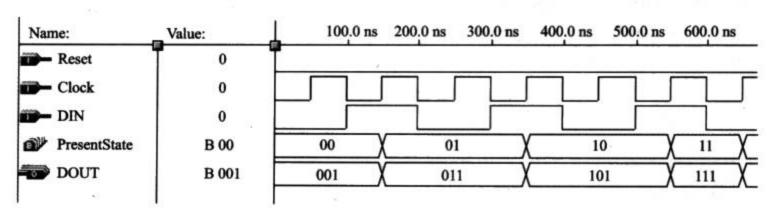

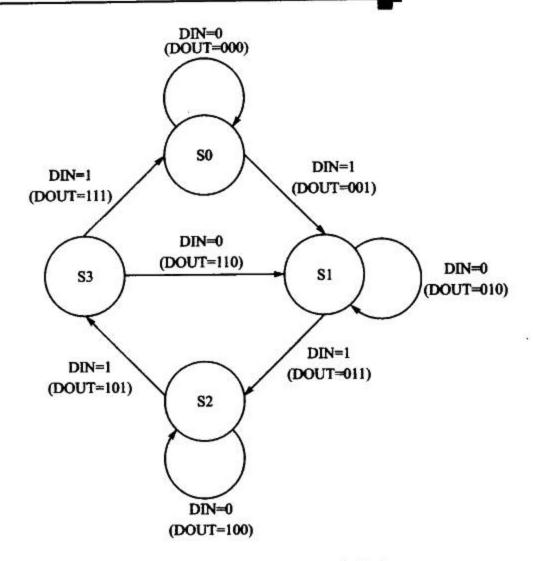

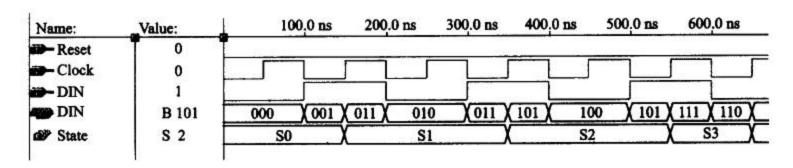

|          |      | . 1   |        |            |                                              |              |       |      |                                         | 描述                                      |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          | DF65 | . 2   |        |            |                                              |              |       |      |                                         | 描述                                      |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          | 3.   | . 3   | 8      | 状态         | ₹ ÐLE                                        | 的容           | 错设    | cit  | •••••                                   | •••••                                   | •••     | ••••        | • • • • • | ••••  | • • • •   | ••••      | •••••   | ••••      | • • • •   | ••••  | • • • • • | •••••     | ••••        | ••••        | ••••• | 72  |

| 第        | 4    | 1     | t      | 系          | 充层                                           | 次化           | 化设i   | H    |                                         |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

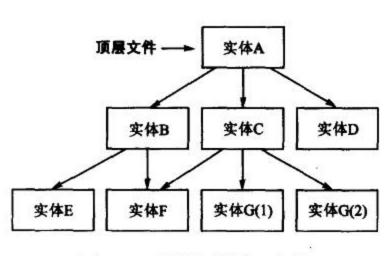

|          | 4.   | 1     |        | 层次         | 化i                                           | 设计           | 的標    | 念    | •••••                                   |                                         | •••     |             | • • • •   | ••••  | • • • •   | ••••      |         | ••••      |           |       | · • • • • |           |             |             |       | 74  |

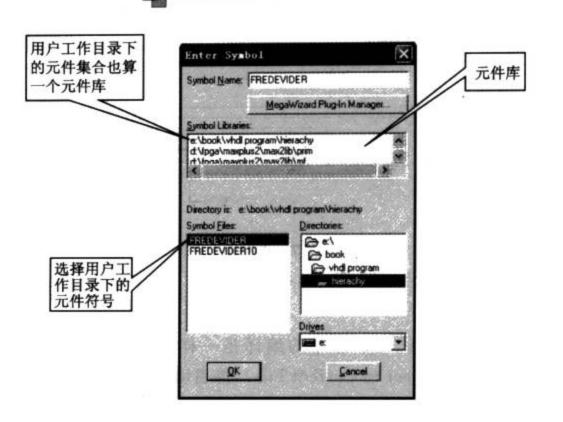

|          |      |       |        |            |                                              |              |       |      |                                         | 现层と                                     |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

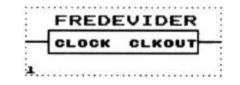

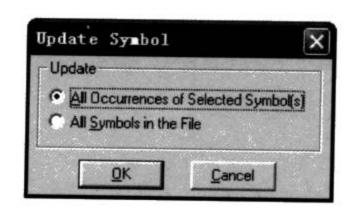

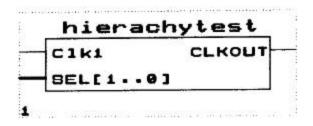

|          |      | 4.    | . 2.   | . 1        | 元化                                           | 中重           | 用…    | •••• | •••••                                   | ••••                                    | •••     | •••••       |           | ••••  | ••••      | ••••      | ••••    |           |           | ••••  |           |           | • • • • • • |             |       | 75  |

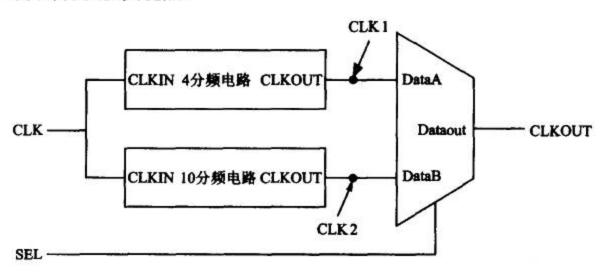

|          |      | 4.    | . 2.   | 2          | 多点                                           | 层次           | 设计    | 的    | 实现                                      | •••••                                   | ••••    | •••••       | ••••      | ••••  | ••••      |           |         |           | • • • • • |       |           |           | ••••        | • • • • •   |       | 79  |

| <b>*</b> | 5    | -     | F      | <b>E</b> 4 | 太尼                                           | Yr 11        | 比设计   | + 14 | ± 84                                    |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          |      |       |        |            | 7. <del>7</del> 33. C. (2)                   | otero te     |       |      |                                         |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          | 5.   | 1     |        | 元件         | 例化                                           | է…           | ••••• | •••  | •••••                                   |                                         | ••••    | •••••       | ••••      | ••••  | ••••      |           | • • • • |           | • • • • • | ••••• | ••••      | •••••     | ••••        | • • • • •   | ••••  | 81  |

|          | 5.   | 2     | 7      | 程序         | 包…                                           | ••••         | ••••• | •••  | •••••                                   | •••••                                   | ••••    | •••••       | ••••      | ••••  | ••••      |           | ••••    | ••••      | • • • • • | ••••• | ••••      | ••••      | ••••        | • • • • • • | ••••  | 84  |

|          | 5.   | 3     | 144    | 类属         | 映身                                           | <b>j</b>     | ••••• | •••  | •••••                                   | •••••                                   | ••••    | •••••       | ••••      | ••••  | ••••      | ••••      | ••••    | ••••      | • • • • • | ••••• | ••••      | ••••      | ••••        | • • • • • • | ••••  | 86  |

| 解        | 形    | ž į   |        |            |                                              |              |       |      |                                         |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

| 第        | 6    |       |        | 初含         | 全者                                           | 常贝           | 门间署   | 重包   | 坐                                       |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|          |      |       |        | (A)        | 25/65                                        | es de        |       |      |                                         |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

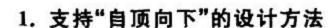

|          | 3.   | 1     | 7      | 关于         | 设ì                                           | 方            | 去…    | •••• | •••••                                   | ••••••                                  | •••     | •••••       | ••••      | ••••• | ••••      |           | ••••    | ••••      | ••••      | ••••• | ••••      | • • • • • |             | ••••        | ••••  | 91  |

| ٠٠,      |      |       |        |            |                                              |              |       |      |                                         |                                         |         |             |           |       |           |           |         |           |           |       |           |           |             |             |       |     |

|    | 6.   | 2    |      | 于信号与变量                                      |                                         |

|----|------|------|------|---------------------------------------------|-----------------------------------------|

|    | 6.   | 3    |      | 于顺序语句的顺序性                                   |                                         |

|    | 6.   | 4    |      | 于仿真与综合                                      |                                         |

|    | 6.   | 5    | 关于   | F MAX+plus II                               | 100                                     |

|    |      |      |      |                                             |                                         |

| 实  | Ø    | 無    | 1    |                                             |                                         |

| 第  | 7    | 章    | *    | 用电路的 VHDL 程序                                |                                         |

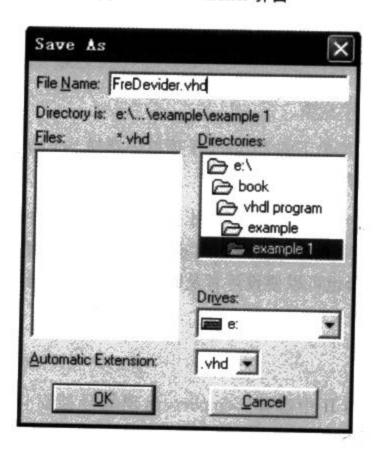

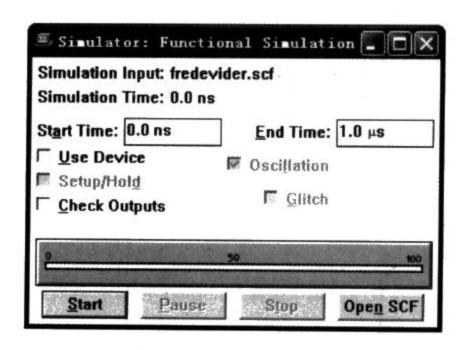

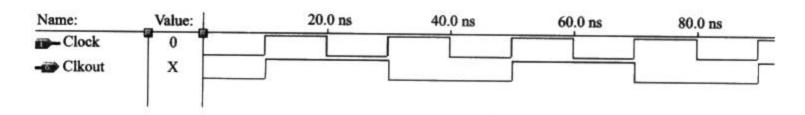

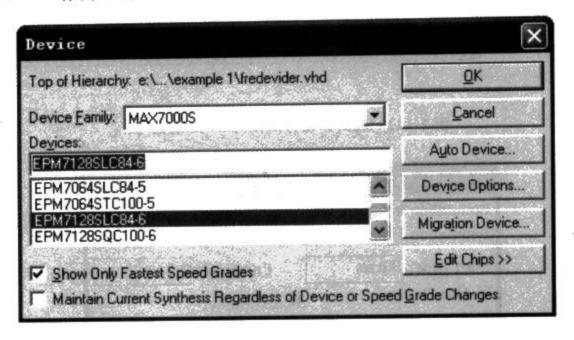

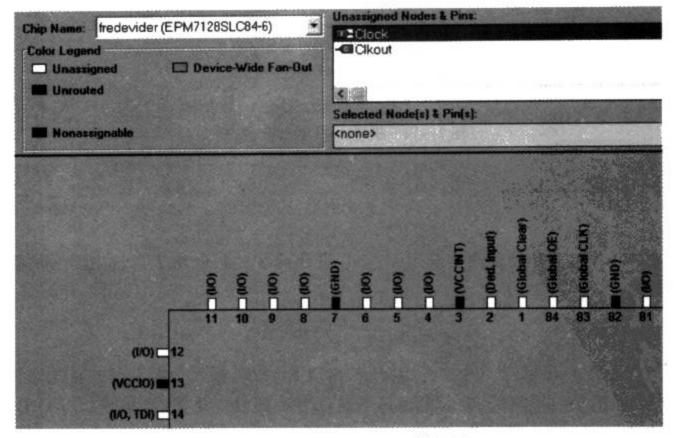

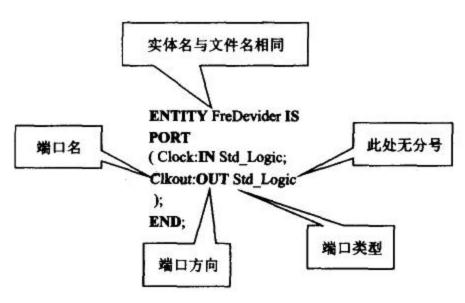

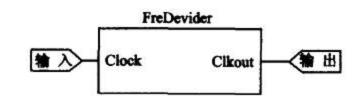

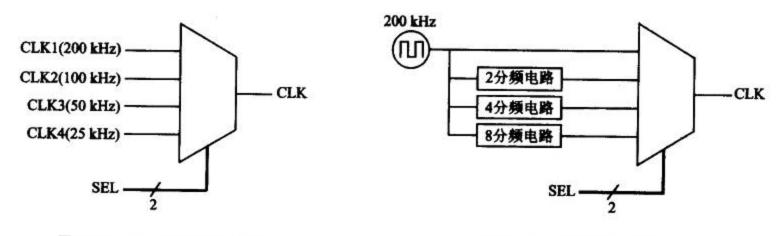

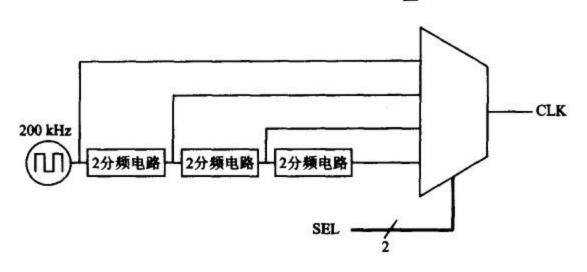

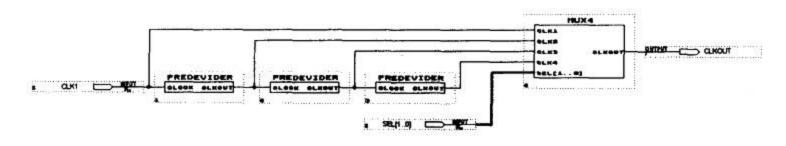

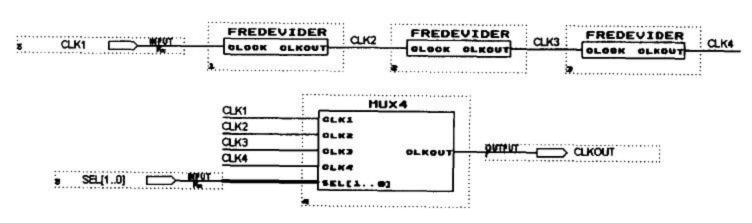

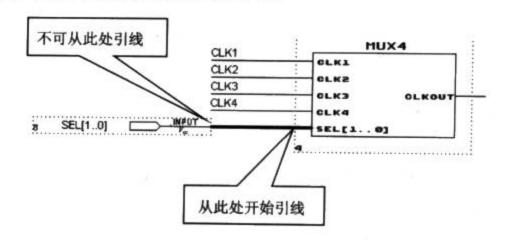

|    | 7.   | 1    | 分步   | <b>页电路</b>                                  | 105                                     |

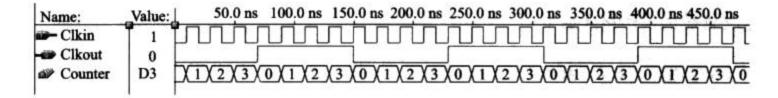

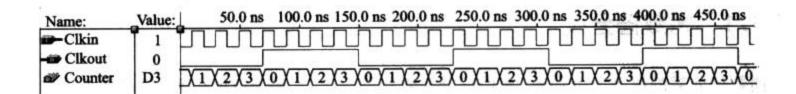

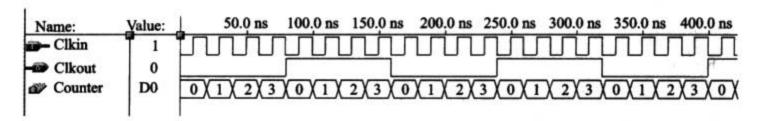

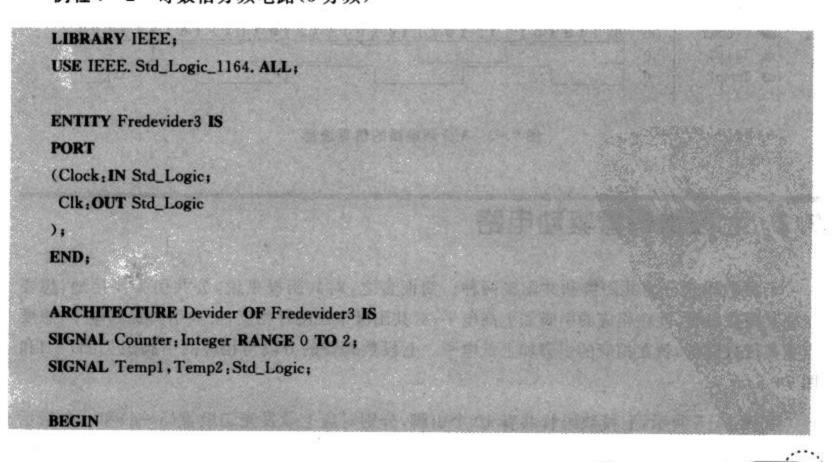

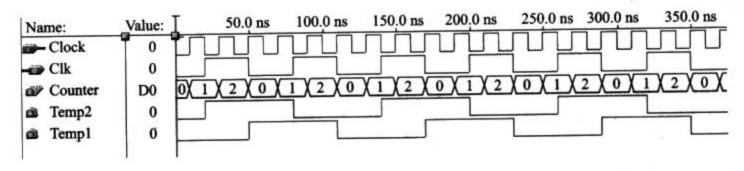

|    |      | 7.   | 1.1  | 偶数倍分频                                       | 105                                     |

|    |      |      | 1.2  | 4 20 III 20 20                              | 2000000                                 |

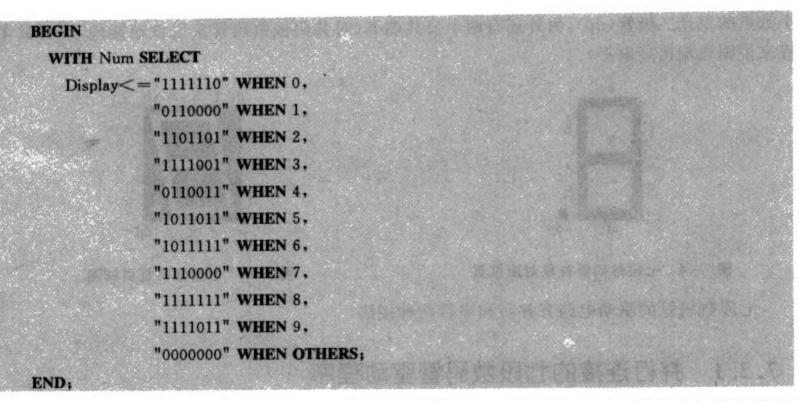

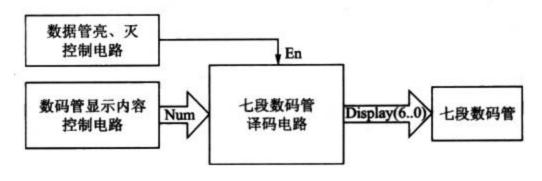

| 88 | 7.   | 2    | 七县   | <b>设数码管驱动电路</b>                             | 2007/07/09                              |

|    |      | 7, 2 | 2. 1 | 并行连接的七段数码管驱动程序                              | 109                                     |

|    |      | 7. 2 | 2. 2 | 1112011000111                               |                                         |

| 33 | 7.   | 3    |      | a.扫描电路 ···································· |                                         |

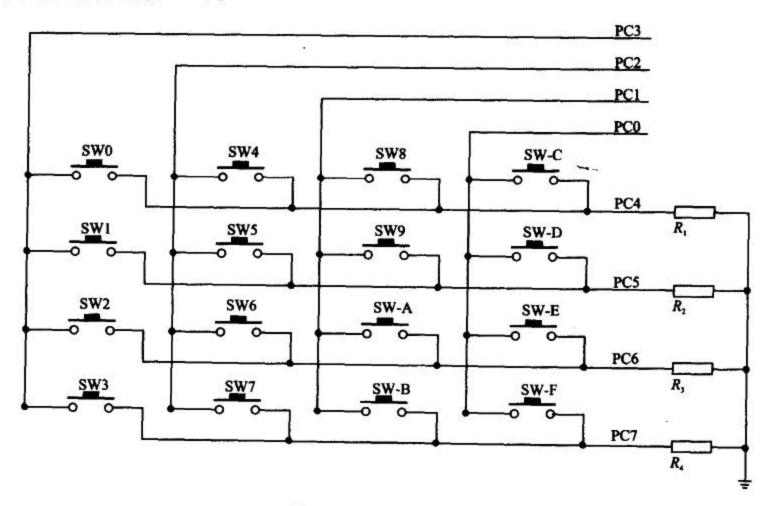

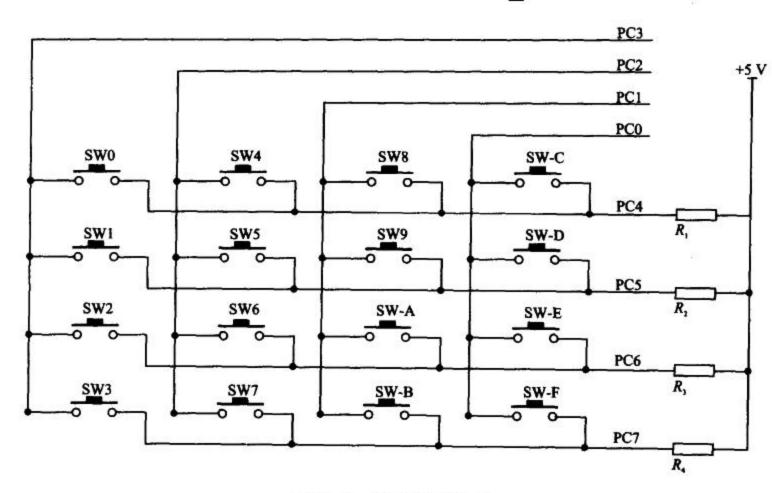

| 88 | 7.   | 4    |      | a.消抖电路 ···································· | 200000000000000000000000000000000000000 |

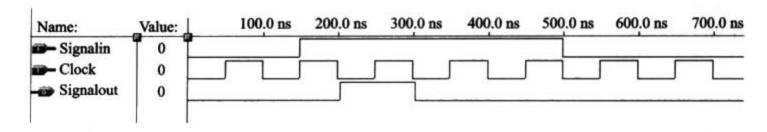

|    | 7.   | 5    |      | ·整形电路 ······                                |                                         |

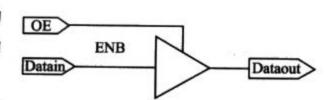

|    | 7.   |      |      | 5缓冲器 ····································   |                                         |

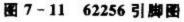

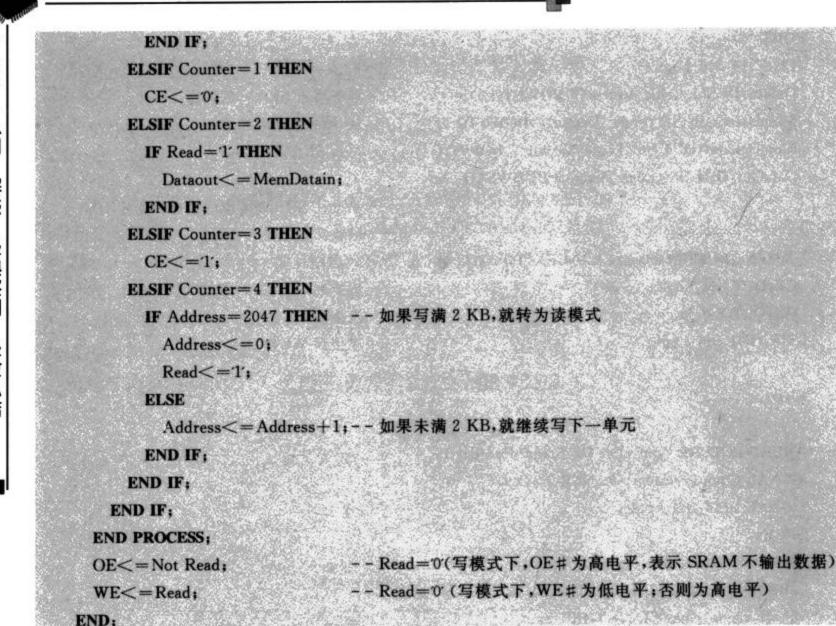

|    | 7.   | 7    | SRA  | AM 控制电路 ······                              | 126                                     |

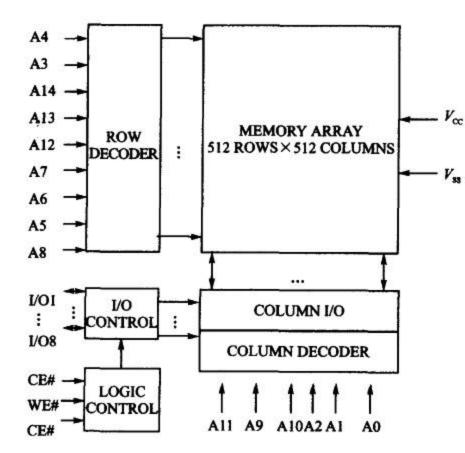

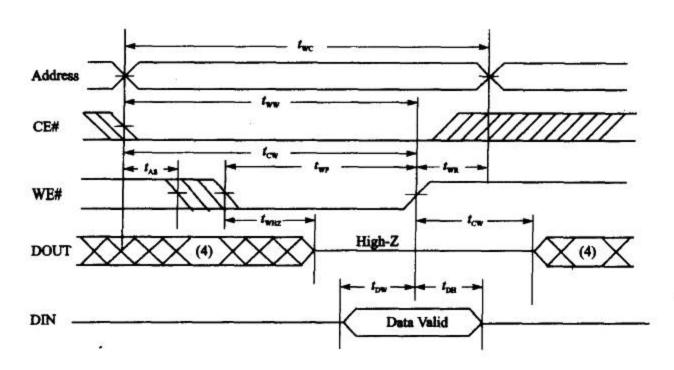

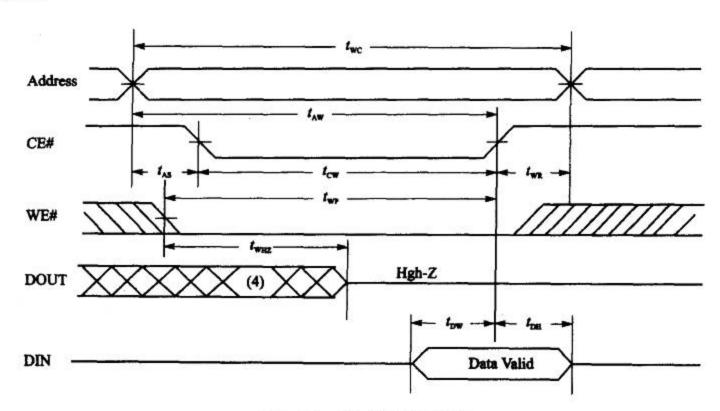

|    | 1    | 7. 7 | . 1  | SRAM UT62256 的读/写时序说明                       | 127                                     |

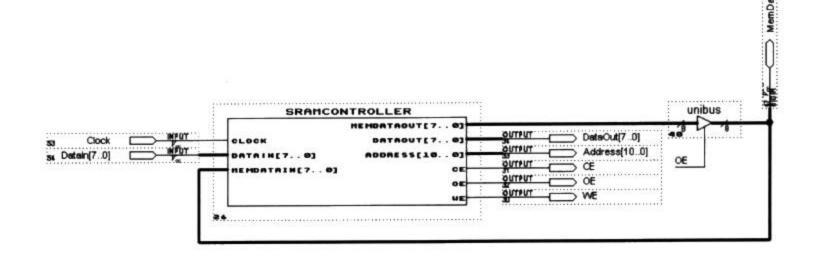

|    | 1    | 7. 7 | . 2  | 用 CPLD/FPGA 控制 SRAM 的读/写                    | 130                                     |

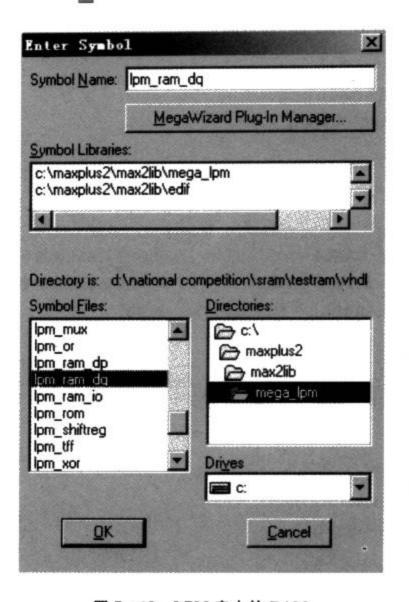

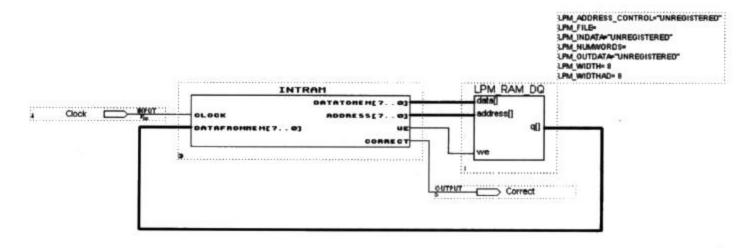

| 1  | 7.8  | 8    | Flex | k10K10 内部 RAM 的读/写 ·······                  | 132                                     |

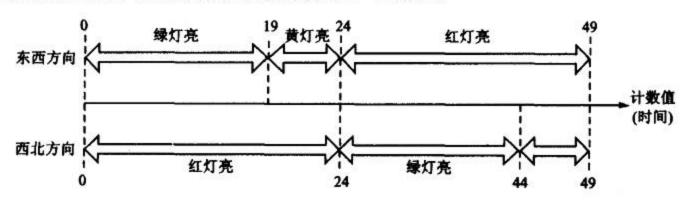

| 第  | 8 i  | ŧ    | 交    | 通灯控制器                                       |                                         |

|    |      |      |      | 书                                           |                                         |

| 8  | 3. 2 | 2    | 参考   | 设计                                          | 137                                     |

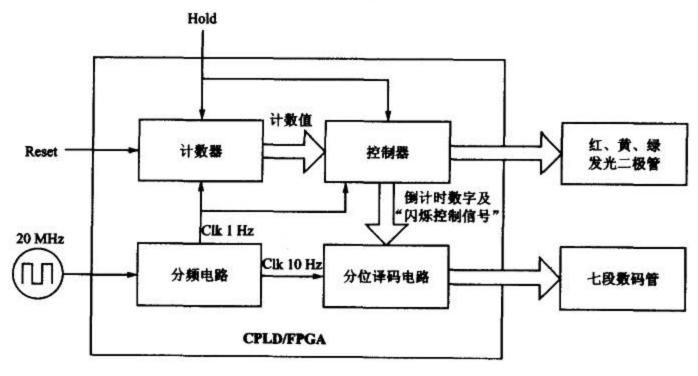

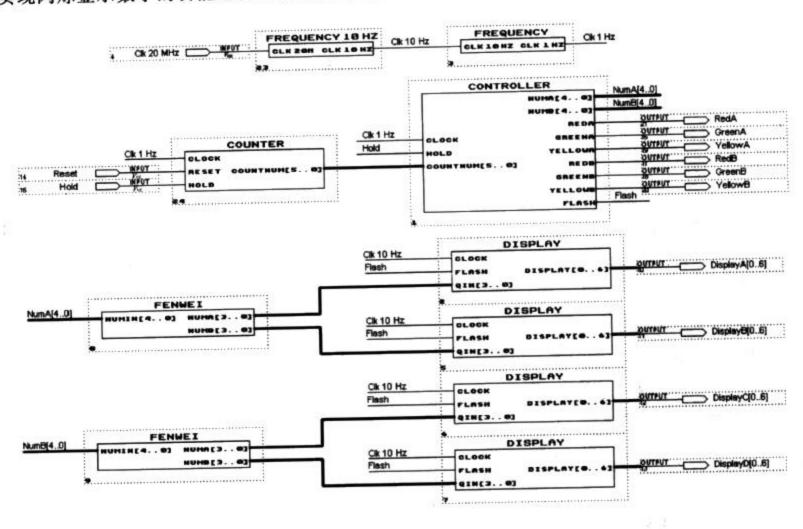

|    |      |      |      | 系统框图                                        |                                         |

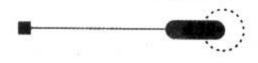

|    | 8    | 3. 2 | . 2  | 计数器的设计                                      | 138                                     |

|    | 8    | 3. 2 | . 3  | 控制器的设计                                      | 139                                     |

|    | 8    | 3, 2 | . 4  | 分位译码电路的设计                                   | 141                                     |

|    |      |      | . 5  |                                             | 143                                     |

| 8  | 3. 3 |      |      | 题                                           |                                         |

|    |      | . 3. | . 1  | 用状态机实现交通灯控制器                                | 143                                     |

|    | 8    | . 3. | . 2  | 计时秒表                                        | 143                                     |

| 第9章 乒        | <b>乓游戏机</b>                                   |         |

|--------------|-----------------------------------------------|---------|

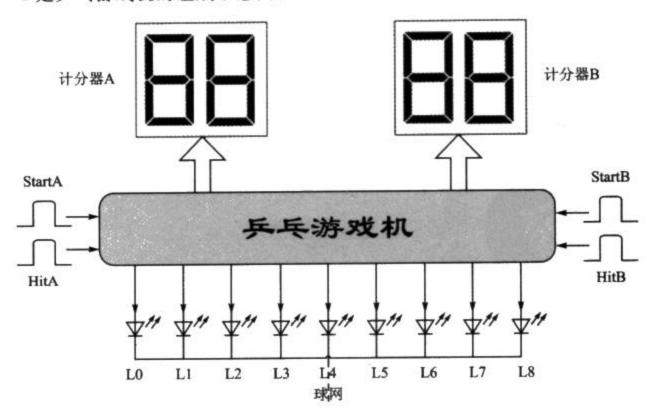

| 9.1 任务       | 书                                             | 144     |

|              | 设计                                            |         |

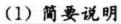

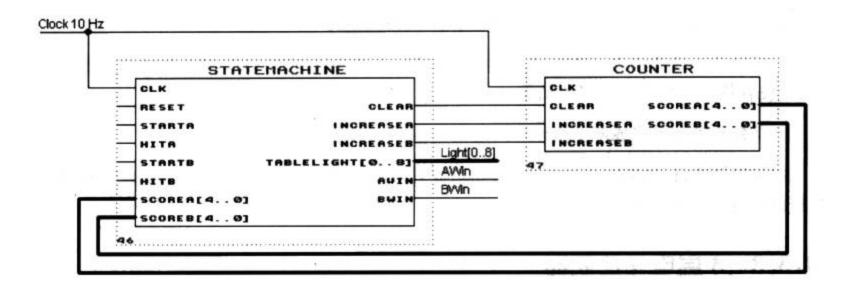

| 9. 2. 1      | 系统框图                                          |         |

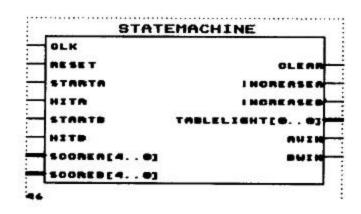

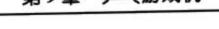

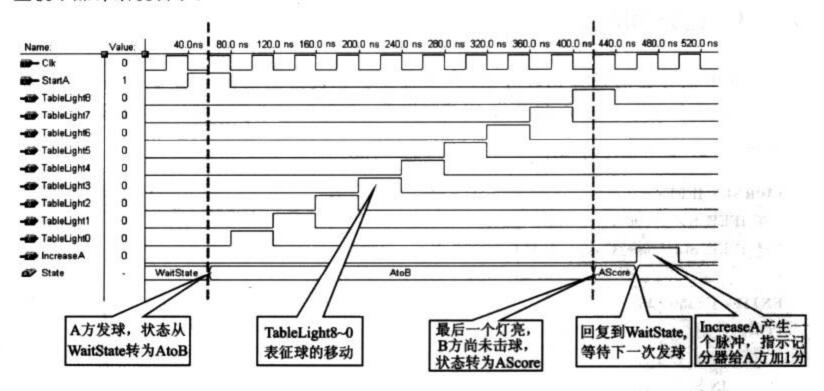

| 9.2.2        | 状态机的设计                                        | 146     |

| 9.2.3        | 记分器的设计                                        | 152     |

| 9.2.4        | 顶层文件元件连接图                                     | 153     |

| 9.3 练习       | 题                                             | 154     |

| 9.3.1        | 乒乓游戏机功能扩展要求                                   | 154     |

| 9.3.2        | 经典数学游戏——过河                                    | 154     |

| 9.3.3        | 3 层电梯控制器                                      | 154     |

| 第10章 数       | 字频率计                                          |         |

| 10 1 / / /   | e Tr                                          | 292     |

|              | 5 书····································       |         |

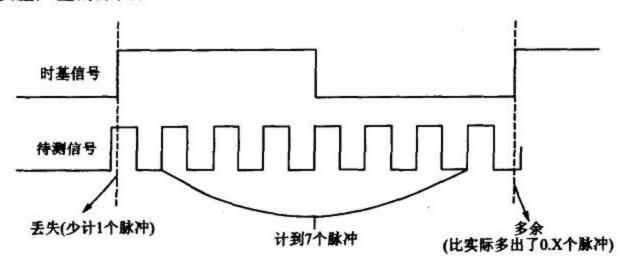

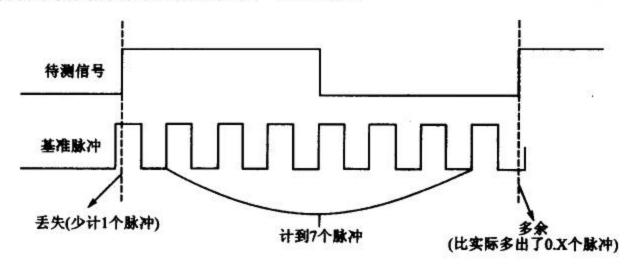

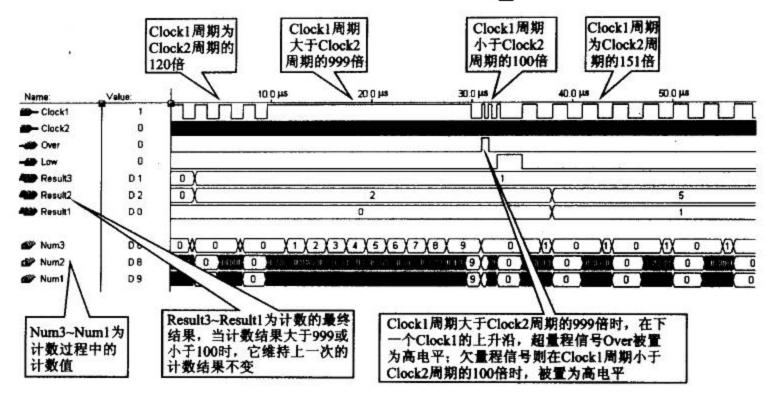

|              | 終与周期的測量原理···································· | F-4761A |

| 10. 2. 1     | <b>测频的原理</b>                                  |         |

|              | 测周期的原理····································    |         |

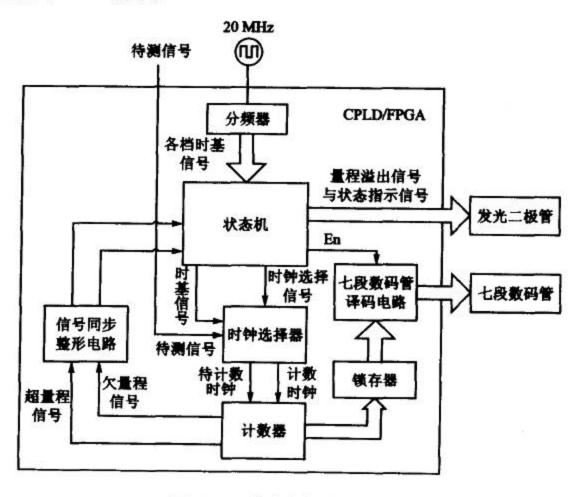

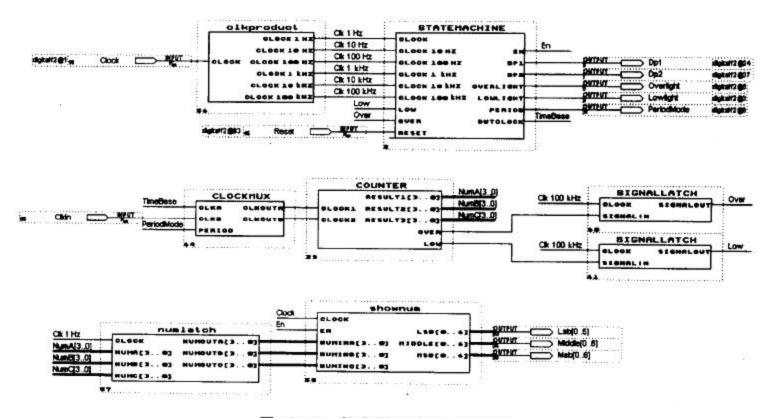

| 10.3         | 系统框图·······                                   |         |

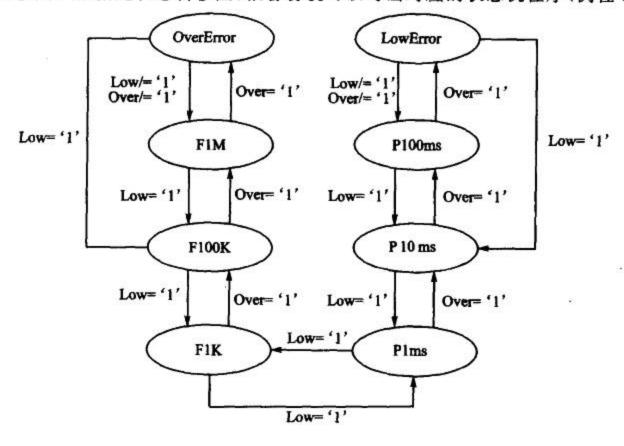

| 194 NY 08584 | 状态机的设计                                        |         |

|              | 计数器的设计                                        |         |

|              | 顶层文件元件连接图                                     |         |

|              | ]题                                            |         |

|              | 洗衣机控制器                                        |         |

|              | 数字钟                                           |         |

| 10. 1. 5     | X 1 M                                         | 170     |

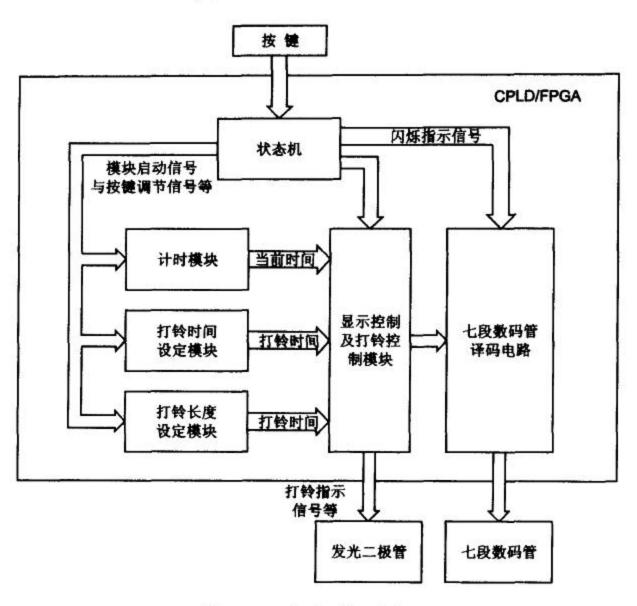

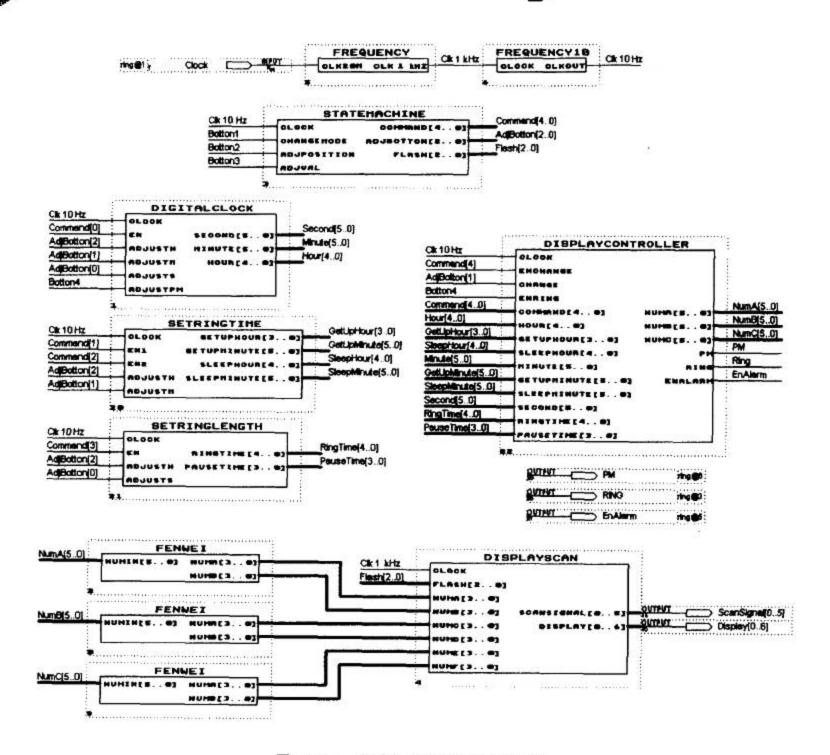

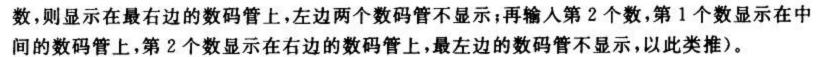

| 第11章 自       | 动打铃系统                                         |         |

| 11.1 任务      | }书                                            | 171     |

|              | f设计······                                     |         |

|              | 系统框图                                          |         |

| 11, 2, 2     | 状态机的设计                                        | 173     |

|              | 计时/调时模块的设计                                    |         |

| 11.2.4       | 打铃时间设定模块的设计                                   | 181     |

|              |                                               |         |

| 11. 2. 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 打铃长度设定模块的设计                                       | 183                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------|

| 11. 2. 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 显示控制及打铃控制模块的设计                                    | 184                                     |

| 11. 2. 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 其他模块的设计                                           | 188                                     |

| 11. 2. 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 顶层文件元件连接图                                         |                                         |

| 11.3 练习                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 题                                                 | 192                                     |

| 第 12 音 W(                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CDMA 短码生成器                                        |                                         |

| A 70 COLORO COLO |                                                   |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 书                                                 |                                         |

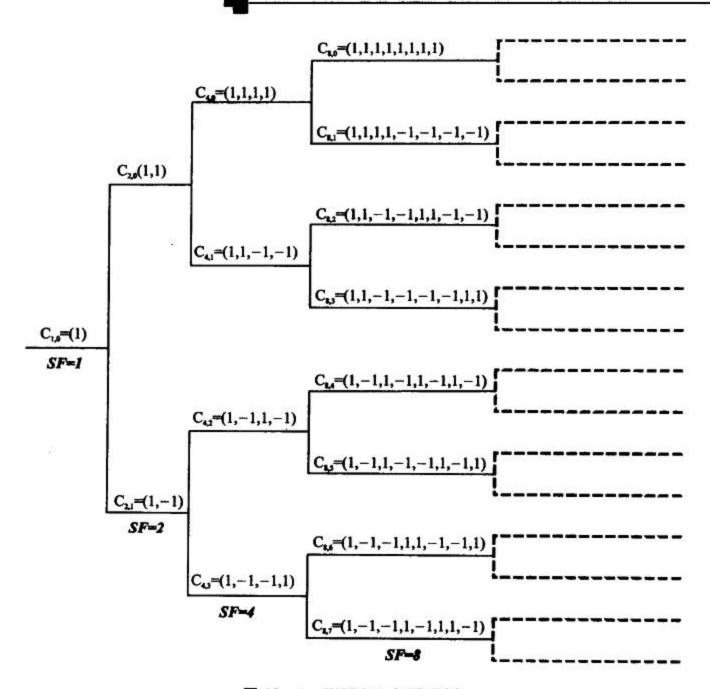

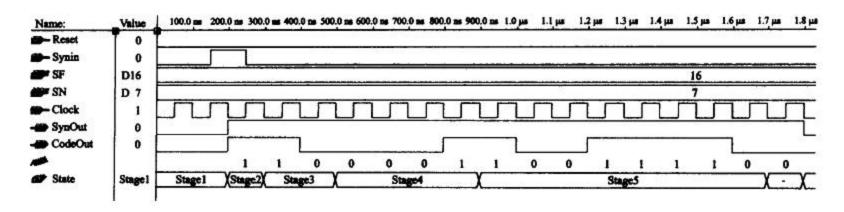

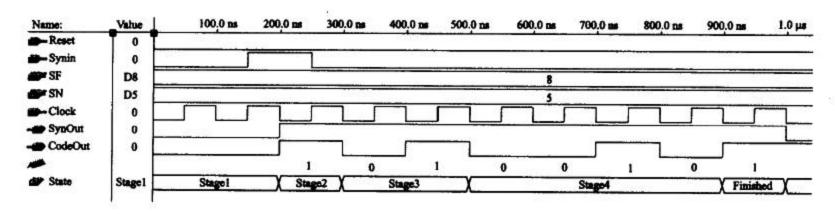

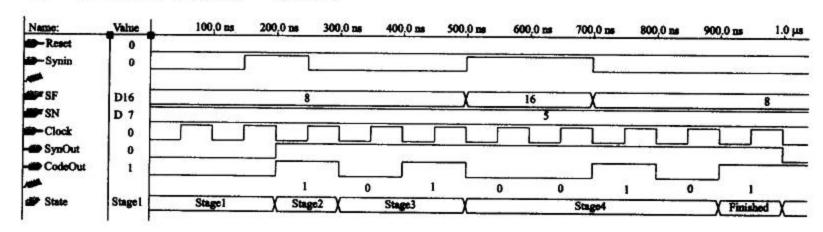

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 设计                                                |                                         |

| 12.3 练习                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 题                                                 | 204                                     |

| 第 13 章 Fra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | naszek 编/译码器                                      |                                         |

| 13 1 任久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 书                                                 | 200                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 设计                                                | 100                                     |

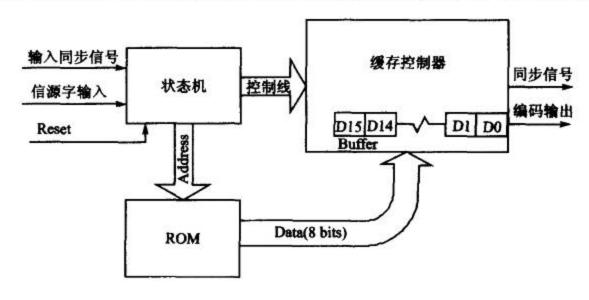

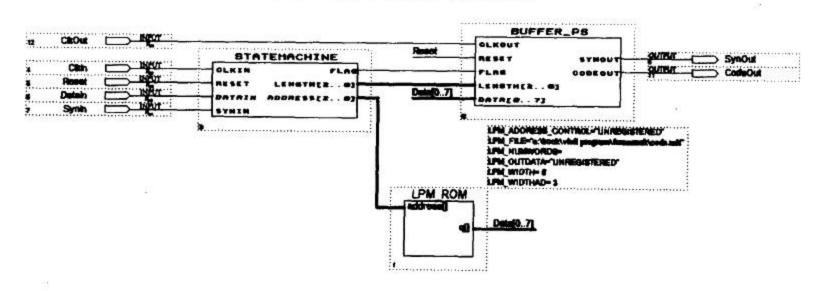

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 总体方案设计                                            | 7-3-3-1-1-1-1                           |

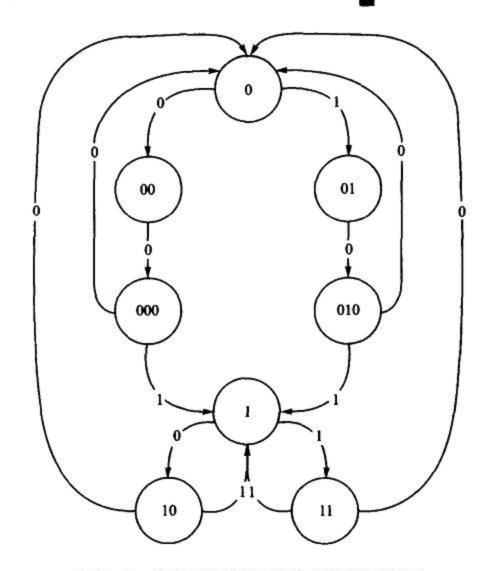

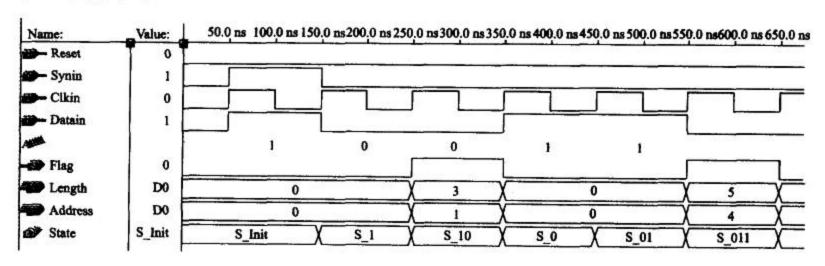

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 状态机的设计                                            |                                         |

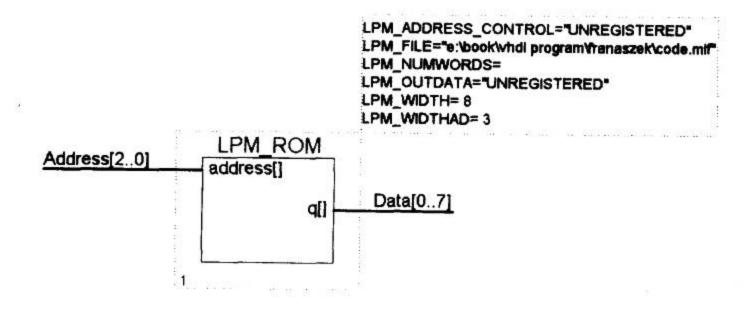

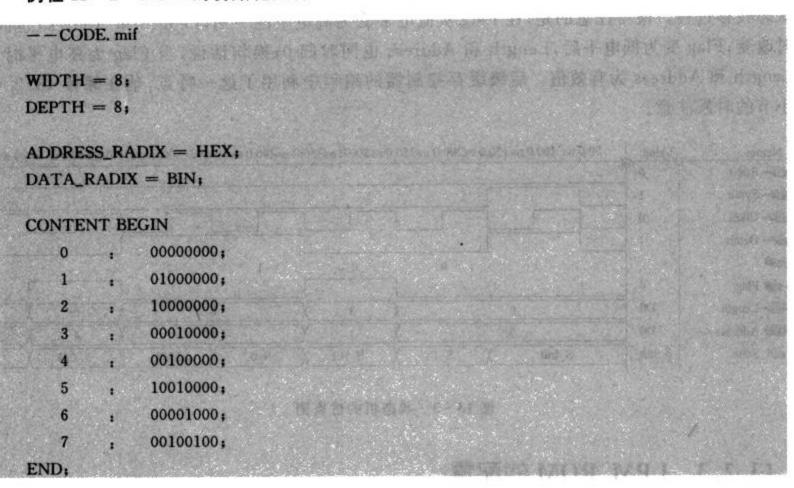

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LPM_ROM 的配置                                       | V 1000000000000000000000000000000000000 |

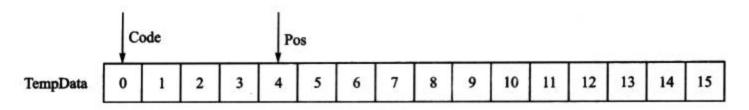

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 缓存控制器的设计                                          |                                         |

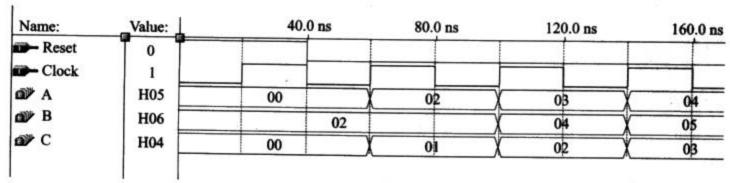

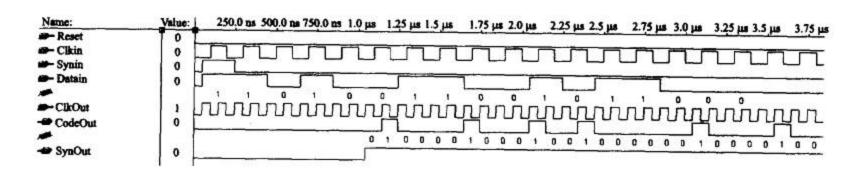

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 顶层文件波形仿真                                          |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 题                                                 |                                         |